- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

How can I make sure that the incoming data from memory is the response to memory read request and is also valid?

I am using Avalon Memory-Mapped Interface and I want to get a valid signal for each data that I request from memory by a readdata request.

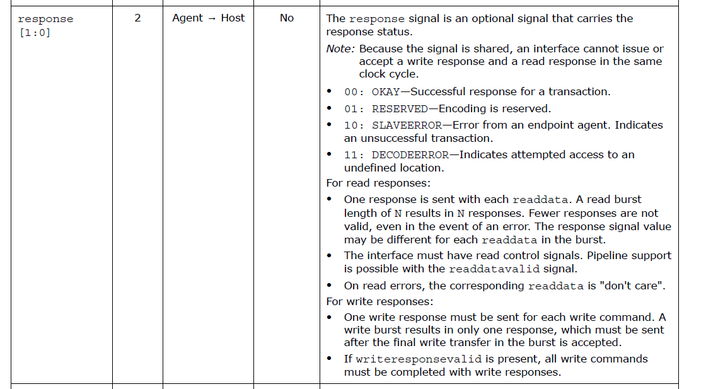

Can I use this condition: (response == 0)? Does it arrive at the same clock that data arrives?

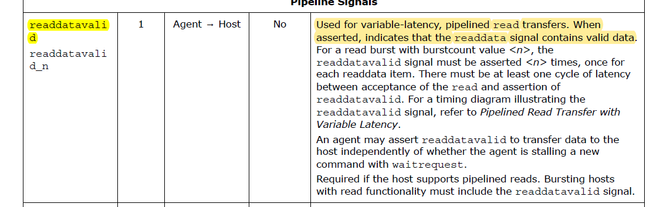

Note that I am using a fixed-latency read, so I am not able to use readdatavalid signal.

Thanks,

Mahdi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, a response of 0x0 can be sent along with valid readdata. Check the info "For read responses" in that table.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, a response of 0x0 can be sent along with valid readdata. Check the info "For read responses" in that table.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Since the issue addressed had been resolved.

I'll now transition this thread to community support.

If you have a new question, feel free to open a new thread to get the support from Intel experts.

Thank you.

Best regards,

Sheng

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page