- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

our data width requirement is 64 bit but Avalon interface has datawidth of 128 after generating ddr3 controller ip.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sbala31,

Thank you for joining this Intel Community.

I assume right now your DDR3 DQ = 16 bits (Quarter rate) and this will provide Avalon (amm) data wide of 128 bits. Also, are you using hard interface?

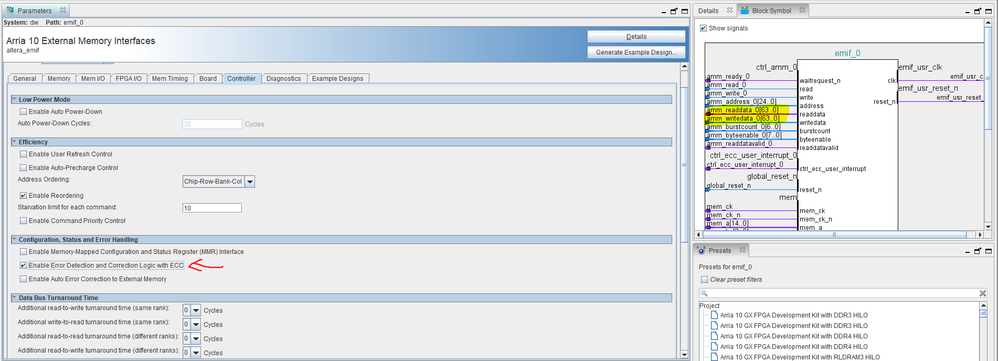

If above assumption is correct, then to have the amm data width requirement, you have to tick “enable error detection and correction logic with ECC” in your EMIF GUI (see screenshot below). After this tick, it will convert the amm data width from 128 to 64 bits (refer to block diagram highlighted in yellow).

For 16 bits interface, usually the extra 8 bits is user for error detection and we only use 8 bits for data. For more details about the Error Correction Code (ECC), you may refer to this EMIF Handbook Vol.3 in below link, search for ECC :

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/external-memory/emi_ip.pdf

Another option is you can reduce the DDR3 DQ width to 8 bits without enabling the ECC. So, either make the interface 8 bits wide or keep it as 16 bits wide and enable ECC to get the amm data width requirement (64 bits).

I sincerely hope this helps. 😊

Thanks

Regards

Aida

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using ddr3 softIP with ecc enabled. But the datawidth of Avalon is 128 bit only for 64 bit ddr3 controller. In this case, how can we change the datawidth of Avalon?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sbala31,

I'm sorry for misunderstood your inquiry at the first place. I thought you wanted to have avalon interface of 64 bits wide.

Unfortunately, the ECC is only available in 16, 24, 40 and 72 bits. If you want to enable ECC, then you need to increase your DDR3 data width to 72 bits or else maintain the DDR3 DQ width to 64 bits without enabling the ECC . This information also covered in the EMIF handbook that I shared in previous thread.

I am truly sorry for the inconvenience caused.

Thanks

Regards,

Aida

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

we have generated 64 bit ddr3 controller softIP(with ECC). for this avalon interface input data width is shown as 128 bit.whether can we change 128 bit to 64 bit datawidth for avalon . so that data processing at avalon interface side will not be complicated.so please suggest if any option is there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sbala31,

Sorry for the delay in response.

Unfortunately, there is no other option as the avalon width is depend on the DDR3 data width. Like I mentioned in previous thread, you need to either increase or decrease your DDR3 data width in order to have your required avalon input data width.

Again I am so sorry for the inconvenience caused.

Thanks

Regards,

Aida

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page