- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

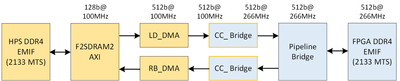

We are using Stratix 10 SX dev kit. Our design is based on the golden reference design from [1] below. In our design, we added the following block, to transfer data between HPS DDR and FPGA DDR using 2 mSGDMA, i.e. LD_DMA for load operation HPS -> FPGA and RB_DMA for readback operation FPGA -> HPS.

In the Linux app, we performed the following transfers:

step 1: LD_DMA: rd_addr=0x6000_0000(HPS), wr_addr=0x8000_0000(FPGA), size=0x80_0000(8MB)

step 2: RB_DMA: rd_Addr=0x8000_0000(FPGA), wr_addr=0x6080_0000(HPS), size=0x80_0000(8MB)

However, we observe strange behavior for RB_DMA. The starting read address sometimes changed to 0x0 instead of 0x8000_0000, right before the reading occurs (see attachment 3). But sometimes, the load value is correct (see attachment 2). For RB_DMA side, there is no issue at all and both read and write address are loaded correctly (see attachment 1).

Have someone experienced this? What could go wrong? Thank you for the help.

[1] https://rocketboards.org/foswiki/Documentation/Stratix10SoCGSRD

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Please use the updated link as given below

https://rocketboards.org/foswiki/Documentation/Stratix10SoCGSRD

Also please let us know the tool version , linux kernel version and other related software versions being used.

Thanks and Regards

Anil

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page