- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel Support and Expert

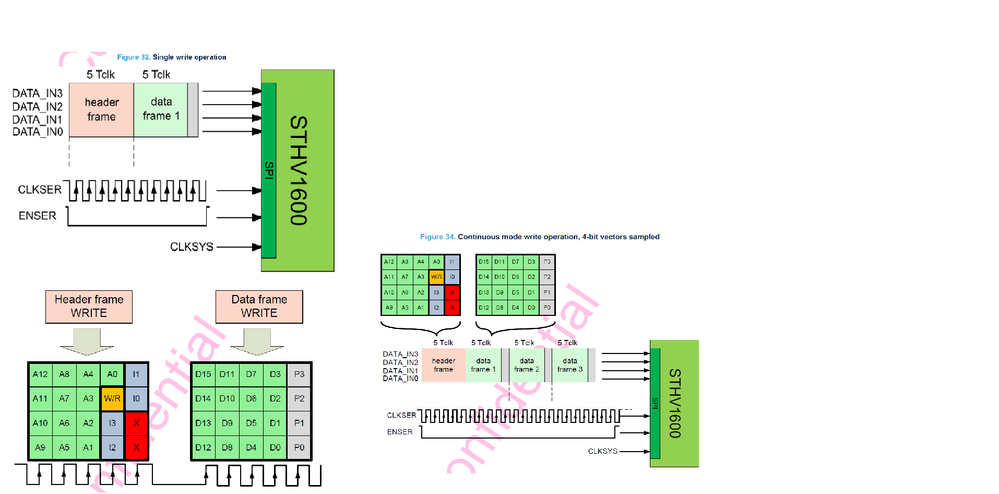

I am working on a QSPI project, the target device is STHV1600 from ST. the chip control is like QSPI, but I think need some customization.

If there is no QSPI IP core that I can use directly. is it possible to make some modification of a standard QSPI core? I hope it will save some time if there is someone already invented the wheel.

Appreciate your help. happy holiday,

David

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Not sure if you are able to use https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-gen-sfi.pdf? I don't think you are able to modify the QSPI Core IP as it is part of the Quartus IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John

thank you for the reply, if there is no similar core that I can use, is there a solution that use the NiosII IO to emulation a Quad-SPI? if true, is there are example how to use NiosII implement an SPI through the IO pin instead of a SPI MASTER core.

Best Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may refer to https://community.intel.com/t5/FPGA-Wiki/Avalon-MM-to-Software-Programmable-SPI-Master/ta-p/735224 example design.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page