- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I want to develop a system with NIOS II Processor on Arria V of one of our custom boards for DDR3 memory transfers.

where as there will be a sensor which will be giving around 128 bit data per clock cycle, and that data we want to transfer to DDR3 on our board itself using SGDMA and NIOS II processor and after that we wanted to read the data also from DDR3 using NIOS II and SGDMA to a USB connection which is connected to FPGA.

Can you help us in finding a sample design in this point of view where as data transfer happens using SGDMA and NIOS II between FPGA and DDR3?

Its been important for us to complete this but couldn't able to find any correct design as example for this as starting point to us.

By the way I am new to quartus where as our previous development used to go with Xilinx(vivado).

Please help us in fastening our development process by providing some useful tutorials and links to solve the above mentioned task.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, you should check the devkits web page of Intel fpga as they provide design examples for almost every on board peripherals.

For example, a CycloneV E with DDR3 :

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Also you may refer to Intel FPGA wiki that consist some generic MSGDMA and EMIF design.

Hope this helps.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Got the example for arria 10 with NIOS using MSGDMA from the following link

https://fpgawiki.intel.com/wiki/MSGDMA_design_example#Steps_to_Run_Design_Example

and I have another example for cyclone V for DDR3 test using NIOS processor SoCkit_v.2.0.1_SystemCD.zip

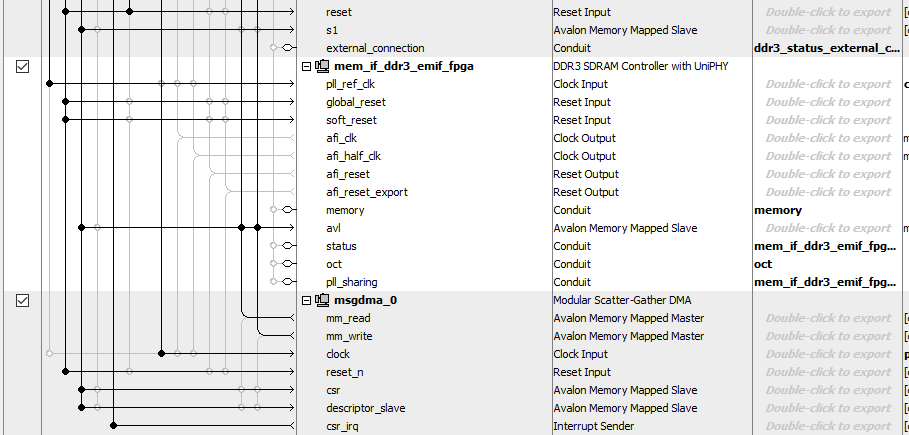

I tried to integrate both.

Things which are working are

- NIOS II <---> DDR3 communciton

- MSGDMA <---> OnchipMemory

- NIOS II <---> OnchipMemory

Things which are not working are

- MSGDMA <---> DDR3 communication

Technically I don't see any problem in my code or project and connections realted but why DDR3 communication not working not getting because even MSGDMA registers also in NIOS Debug for both case MSGDMA to onchipmemory and MSGDMA to DDR3 are responding in the same way. But, don't know why writing to DDR3 using MSGDMA is not working. Any idea that you can tell for this...?

Zip file of the project also has been attached . You can review it once and help us.

The FPGA kit we are using for this test is available in the following link for your reference.

https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=205&No=816&PartNo=2

You can review our design once and help us in correcting it if there is any mistake or error?

Awaiting for your reply.

Hope we will get the help soon.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Vsath1,

Please allow me some time to look into your issue. I shall come back to you with finding.

Thank you for your patience.

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vsath1,

I can give you idea on how to debug the issue. I will suggest you signaltap (stp) the avalon-MM interface (interface between DDR3 and MSGDMA) and check which signal is not behave unexpected. You can compare the stp waveform with the working design like NIOS II to DDR3.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes.. I will look in that way also and tell you if anything I find.. meanwhile please review the project I have sent and if possible if you have the kit i mentioned you also run once and see the result please. Actually I already enable signal tap also in the project i gave. You can see that also once.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi VSath1,

Just to let you know that we are still working on the design to isolate the root cause. I'll let you know the results once we have done.

Thanks.

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Very nice to hear that from that.

Have to tell one good news. After enabling Signal tap found that there is no transfer happening from NIOS to DDR where as transfer from MSGDMA to DMA is happening and that is because accidentally the DATA_BUS of NIOS is not connected to DDR3_CONTROLLER's AVALON_BUS. Corrected that and generated a new .sof file and then that point onwards it started working. Thanks for the help of giving the idea to solve the problem using signal tap. It helped us.

Regards,

Venkatesh Sathar.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Venkatesh,

Thanks you for sharing the good news and I'm glad to hear that everything is working now at your side now. 😊

You are more than welcome. Feel free to post any update in Intel Forum if you encounter any issue in future. We will try our best to support you.

Thanks and have a nice day !

Regards,

NAli1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page