- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using standard FPGA FFT IP for our design given by intel.

we want to use many FFT IPs parallely for that the problem that we are seeing is resources for ALMs required is not suffiecient with the fpga availability.

It has sufficient amount of dsp available in the fpga.

So, is there any way for that fft ip to consume some of the DSPs in the fpga for some part of logic instead of ALMs so that we can fit more parallel ffts in our design and use all the ALMs and DSPs effectively.

As this is critical for us any answer soon helps us a lot.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

But You can see in your datasheet it will consume DSPs but according to the datasheet also not happening no. Then how the number in the datasheet for DSP consumption given.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you send me the link of the datasheet. I will investigate it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

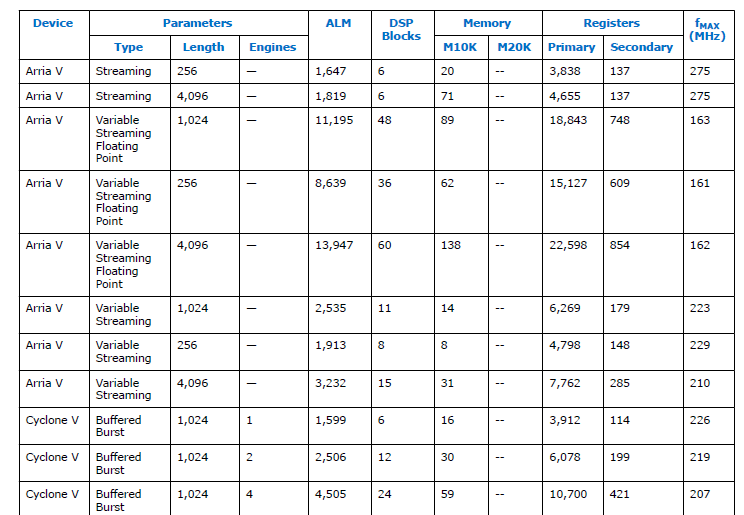

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_fft.pdf

under resource section you can see this table

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It took me few hours to debug it. Seems like your ip is corupted. I recreated it and it is working now. Will attached back your design.qar shortly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

did you recreated it in 16.1.2 quartus standard edition only?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

you created the entire thing with 18.1 tool. I am using 16.1 tool. It's not happening with 16.1 quartus tool. I want the solution for 16.1 tool.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

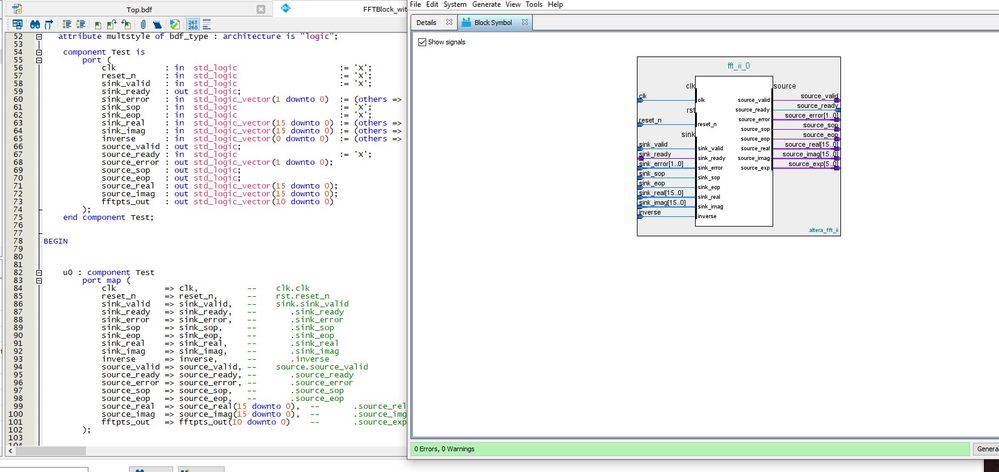

The whole point is that you are doing this project from start with 16.1 something you made in 18.1 downgrading or something like that to 16.1 so it is working. I applied your things in other project of 16.1 and nothing is working , I just saw the synthesis settings to match everything and all are same. still DSP are not getting consumed. In your project given by you also you can see the difference between the component you instantiated and actual block is different of the IP, you can the see in the following picture. If possible please try to create everything from scratch in 16.1 and show me this happen, otherwise no use.

you can source_exp in block diagram but you mentioned fftps_out which is in 18.1 IP component.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, I will recreate this from scratch for Q16.1 tomorrow. Any reason that you cannot upgrade to Q18.1? As this might be an old Quartus bugs.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Our entire project provided by our vendor is with 16.1 only , over that we are developing some algorithms. Looks like vendor right now will not upgarde project to 18.1 with his custom made DSP Builder related IPs etc and give us.So, we are also proceeding with 16.1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I check in Q16.1, it does seems to be a bugs as Q18.1 does not face this issue. What you can do is the follow:

1) download and install Quartus 18.1

2) copy the files from the Q18.1 (<quartus_install_dir>/ip/altera/dsp/) to the Q16.1

This will make your Quartus 16.1 make used of Q18.1 dsp block. As long as quartus able to compiles, the functionality should be fine. However, you have to make simulation to double check.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, you will need to recreate the IP in Q16.1 to make it work, in your project navigators -> Ip components -> double check the IP is using 18.1 version

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

how to make it happen to use 18.1 FFT in 16.1 quartus software. For that also some background folders of the IP in installation need to copy from 18.1 is it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you follow the above steps that given? If you follow the steps, you should not have the question how to make it happened.

Basically, Quartus detect hw.tcl files for all the IP that is using. If you move over the whole dsp folder, all the necessary files will be copied over and you will see it like I mention above.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

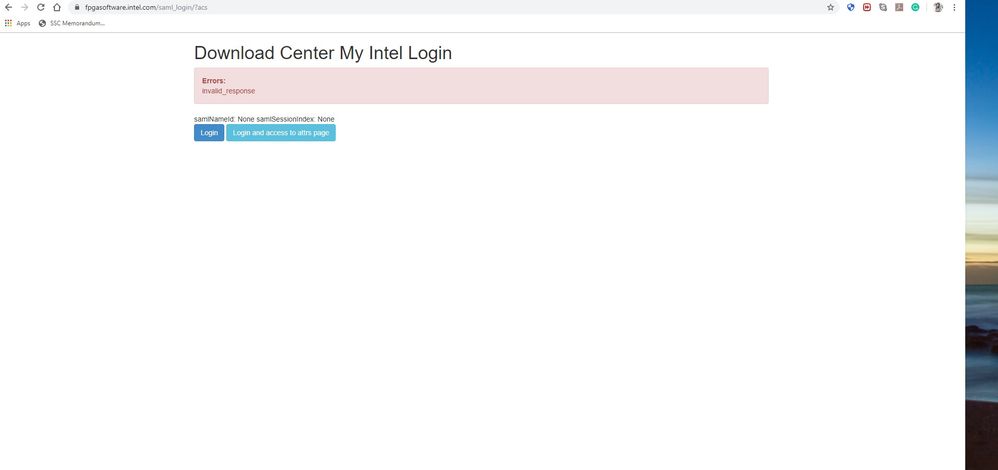

I am unable to download you 18.1 software now i think due to some other problems of your website. because for any account login for download coming like this only. After solving this by you guys only I can try i think so😕

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

seems to be website issue. will get back to you on this

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

we should have fix the website, have you tried?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

downloaded the 18.1 but the actual task not tried yet because the project in 16.1 i was using for some other task, as soon as it finish i will try this and update you here. Sorry for the delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

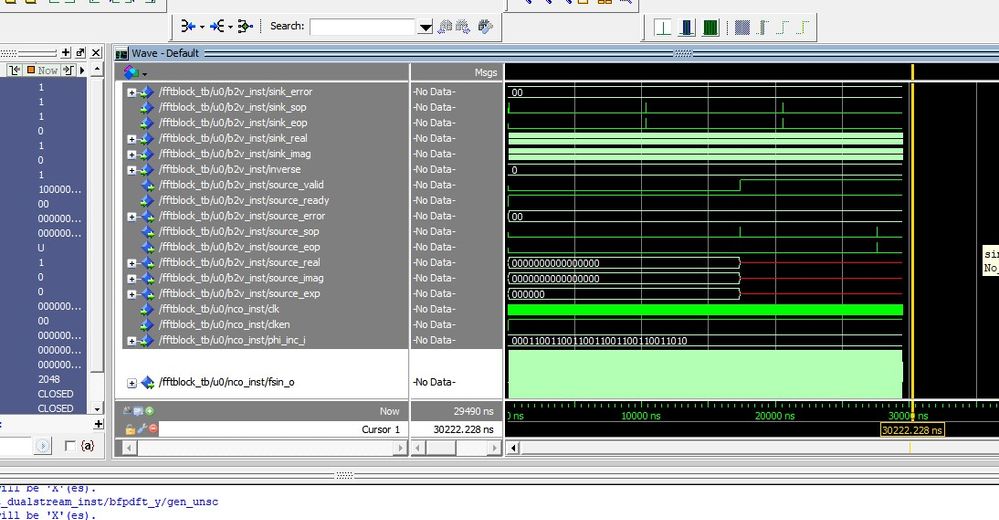

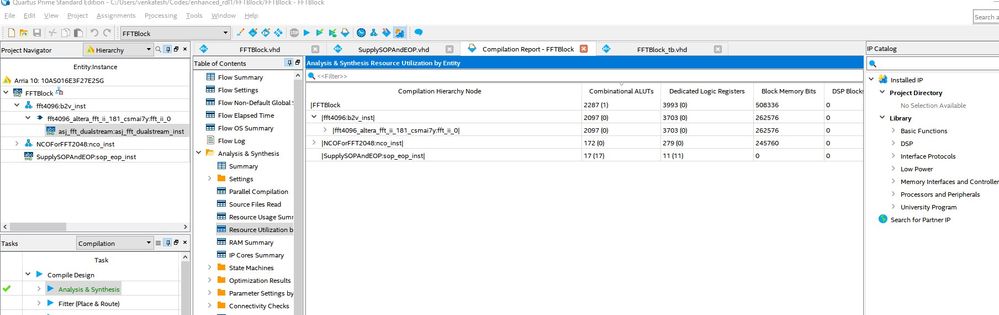

The following is the picture of resource of the example project i have created and it's simulation results. You can see mine for the same configuration consuming only 2k ALMs and no DSPs.

Even the simulation in Modelsim using that also not getting proper results. In my main project also around same 2k resources it's consuming and the result there i am seeing in signal tap and even that project result also from source output all are zeros except the dc bin with some amplitude. I am not getting to know where the problem is happening with this fpga part and why no results producing properly.

To see the simulation in the mentor folder run fftblock.do in modelsim so that you can see the result too. But , whole problem is same that now it's is confirmed for me that my fft ip somehow inside signals getting trimmed whether it is 16.1 or 18.1 even for a sample code and not consuming any dsp and not giving any result.

Please help me in this aspect what is the problem of my project or my settings. By the way I am doing 2048 fft don't get confused with 4096 name and example project you gave also changed to 2048 fft and the resource consumption table shown in last picture.

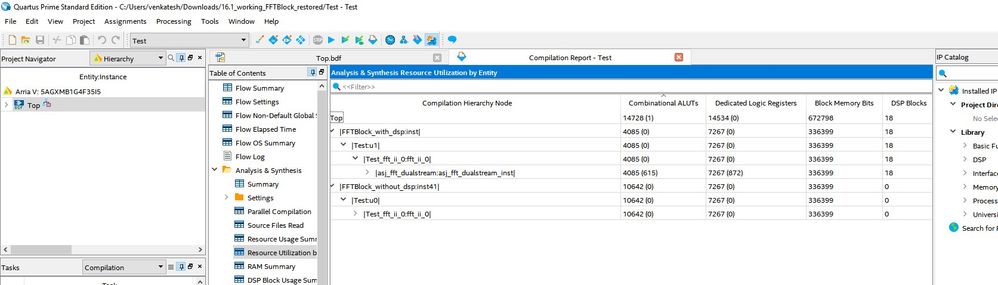

The following is the resource consumption table after synthesis of the example project attached by you previously. You can see FFT with DSP consumes around 4k ALMS and 18 DSPs

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I download your design.zip files. I had few question for you

1) does the design able to simulate using your testbench for Q16.1 fft?

2) Also, I notice that your resource had drop for your FFT. In your screenshot, it show it had about 10000++ ALUT but your design only shows 2097. This means that you have leave your pin float. You cannot leave your pin float as it will optimized a way a lot of logic.

3) Can you make your design when tools -> simulation tools -> rtl simulation works? from my side, if I do that, I see error messages.

4) if your design work for Q16.1fft, can you attached it for me to make comparison as well? I will try it on Q18.1 to see if this can be work or not.

5) you do not need to zip the whole design to send it as it take a lot of spaces. Just project -> archive project and it would be sufficient. please resend your design after you make the changes above.

Please note that you were doing something that I suggest in not a normal way. It will not guaranteed to be work as no one had tested it before. The suggestion is still use the Q18.1 to workaround this bugs.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page