- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

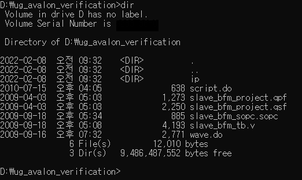

i Tried below Steps using Attached zip files

- Intel FPGA Starter Edition 10.5b (modelsim)

At the step 7, script Line#6

vlog -novopt -reportprogress 300 -work work ./slave_bfm_sopc.v

# ** Error: (vlog-7) Failed to open design unit file "./slave_bfm_sopc.v" in read mode.

# No such file or directory. (errno = ENOENT)

and also cannot download that Intel FPGA That BFM Links.

(PDF / Zip)

Try to Download Zip

The requested URL was rejected. Please consult with your administrator.

Your support ID is: 15434485139140875093

[Go Back]

Try to Download PDF

The requested URL was rejected. Please consult with your administrator.

Your support ID is: 15434485139120367810

[Go Back]

To run the simulation, follow these steps:

1. Start the ModelSim-Altera software.

2. On the File menu, click Change Directory.

3. Navigate to

<working_directory>\ug_avalon_verification\sopc_builder\tutorial_slave_bfm

and click OK.

4. On the Compile menu, click Compile Options.

5. Click the Select Verilog & SystemVerilog tab.

6. In the Language Syntax box, select Use SystemVerilog and click OK.

7. Click Load on the File menu to open the Modelsim script file, script.do.

The script file creates a new working library, compiles all source files, runs

simulation, and loads signals into the Modelsim wave viewer.

If you are running ModelSim-SE you must use the

-novopt

option to prevent

ModelSim from optimizing the design, making the signals specified in for the wave

viewer unavailable.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

The slave_bfm_sopc.v in do file has to changed to slave_bfm_sopc.sopc because there is only slave_bfm_sopc.sopc in ug_avalon_verification file.

Thanks,

Ean

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any update on your problem?

Thank you.

Regards,

Ean

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i tried another way ..

log -novopt -reportprogress 300 -work work ./slave_bfm_sopc.v

-> no exist "slave_bfm_sopc.v" files

log -novopt -reportprogress 300 -work work ./slave_bfm_sopc.sopc

-> modelsim cannot understand .sopc files

so i tried the pdf (Avalon Verification IP Suite, #187)

example Qsys design [avlmm_1x1_verilog.zip]

- Avalon_mm-BFM [M] <---> [S] Avalon_mm-BFM

- Simulation well working like that : Modelsim -> File -> Load -> Macro file... -> run_simulation.tcl

my goal is.. Verification what i designed Avalon mm Slave Logic [.. in progress]

[-----------------------------QSys--------------------------------] [-FPGA Logic for Avalon mm Verification-]

- Avalon_mm-BFM [M] <---> [S] Avalon_mm-Salve [Conduit] <---> Avalon_mm_Interface Logic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think the main problem is lacking of slave_bfm_sopc.v file. You may try to create slave_bfm_sopc.v following the command in the user guide.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's right need to make(Generate) "slave_bfm_sopc.v" file.

as far as i know.. "slave_bfm_sopc.v" file is output of the Sopcbuilder.

But i cannot find Step to Generate

- Such as Generate SopcBuilder,

- Open SopcBuilder

- how to design SopcBuilder

(open "slave_bfm_sopc.sopc" files, there nothings..)

as u can see slave_bfm_sopc.sopc files..

only figure out some clue..

- clk_0 = 50Mhz

- device : STRATIXII

- Software : Quartus 9.1 Version

- Project Name(file) : slave_bfm_project.qpf

output files : Verilog

---------- slave_bfm_sopc.sopc ------Start ----

<?xml version="1.0" encoding="UTF-8"?>

<system name="slave_bfm_sopc">

<parameter name="bonusData"><![CDATA[bonusData

{

element clk_0

{

datum _sortIndex

{

value = "0";

type = "int";

}

}

element slave_bfm_sopc

{

}

}

]]></parameter>

<parameter name="deviceFamily" value="STRATIXII" />

<parameter name="generateLegacySim" value="false" />

<parameter name="hardcopyCompatible" value="false" />

<parameter name="hdlLanguage" value="VERILOG" />

<parameter name="projectName">slave_bfm_project.qpf</parameter>

<parameter name="systemHash" value="-1624089005" />

<parameter name="timeStamp" value="1253262866138" />

<module name="clk_0" kind="clock_source" version="9.1" enabled="1">

<parameter name="clockFrequency" value="50000000" />

<parameter name="clockFrequencyKnown" value="true" />

</module>

</system>

---------- slave_bfm_sopc.sopc ------End ----

To run the simulation, follow these steps:

1. Start the ModelSim-Altera software.

2. On the File menu, click Change Directory.

3. Navigate to

<working_directory>\ug_avalon_verification\sopc_builder\tutorial_slave_bfm

and click OK.

4. On the Compile menu, click Compile Options.

5. Click the Select Verilog & SystemVerilog tab.

6. In the Language Syntax box, select Use SystemVerilog and click OK.

7. Click Load on the File menu to open the Modelsim script file, script.do.

The script file creates a new working library, compiles all source files, runs

simulation, and loads signals into the Modelsim wave viewer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page