- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have made several attempts to make DE0 nano boot from flash (epcs64) with a Nios II and code running from SDRAM. In the mean time I have tried all tutorials, every trick posted over the several years. Using Quartus lite 18.1. Would somebody be so kind to just help or post a bare example (and maybe workflow) of a DE0 nano board booting from EPCS and then run code in SDRAM. ps. I know the hardware is functioning. But the code just won't load. Many thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have done this long time ago. You need to maintain two important things:

1- The clock that feeds the SDRAM should be shifted around -3 nano seconds.

2- Use Older Quartus Programmer version instead of 18.1, for example 15.0

Page 11 of this document shows the PLL time shift to handle the SDRAM timing issue:

This document below, shows how to program the EPCS of DE0-nanop

ftp://ftp.intel.com/Pub/fpgaup/pub/Intel_Material/17.0/Tutorials/DE0-Nano/Using_DE0-Nano_Flash.pdf

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many thanks for your reply and links. I can perfectly run the program in SDRAM form the debugger (eclipse). I can perfectly make a bootable epcs64 system when nios is running from SRAM (and NOT SDRAM). It's the combination of getting it to boot from EPC and rund code/data from SDRAM that is the issue. I know the hardware boots from EPCS.. but for some reason the code isn't loaded into Sram or not booted... all parameters are set correct according to Intel manual... So problem persists

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many thanks for your reply and links. I can perfectly run the program in SDRAM form the debugger (eclipse). I can perfectly make a bootable epcs64 system when nios is running from SRAM (and NOT SDRAM). It's the combination of getting it to boot from EPC and rund code/data from SDRAM that is the issue. I know the hardware boots from EPCS.. but for some reason the code isn't loaded into Sram or not booted... all parameters are set correct according to Intel manual... So problem persists

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have sent you an email for a debug session.

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

My apologize for the late reply. I was looking for a DE0 nano board to test the design, and luckily, I found one. I could test the design on board and its booing from EPCS without any issue.

I will attach the design to help you settle the issue.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fawaz,

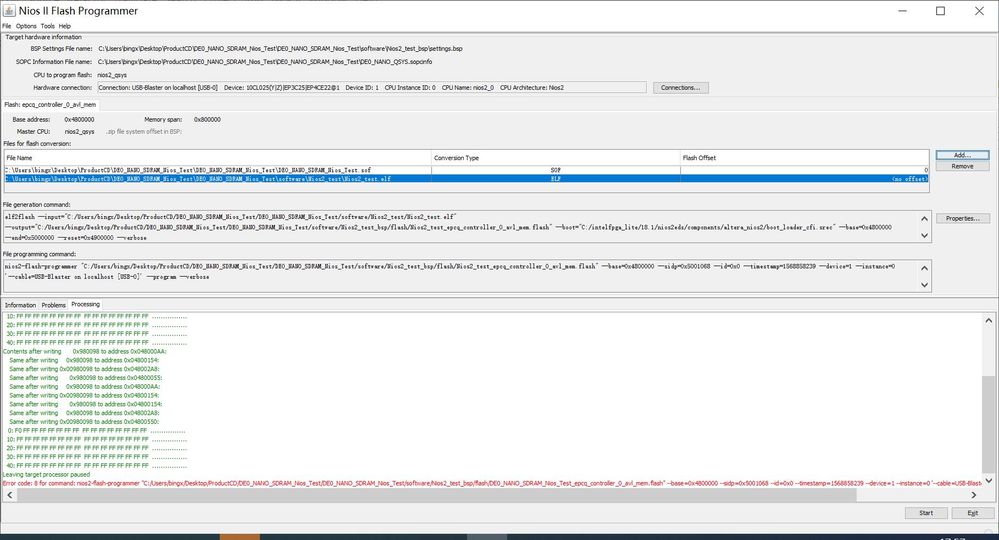

I tested the attached project with my DE0-Nano board, I had a error when using the Flash Programmer to program the EPCS device, could you help checking the issue? I attached the error information here.

By the way, could you teach me how you generated the .jic file for this project?

Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This design works indeed. Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page