I bought A new DK - DEV - 10 cx220 - A, use website kit through the onboard Micro - USB connection is not on the board, dial the code switch is the default state, use multimeter to check, found that U2 EN_GROUP * for low level, makes the power supply chip board part can not make, doubt is U2 record of the program has A problem, need to burn down try U2 pof file, the website not found, do not know can you provide?

链接已复制

Hi Sir

Welcome to INTEL forum. For Cyclone® 10 GX file, you could download it at Documentation>kit Collateral(zip) file in https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/cyclone-10-gx-development-kit.html

Hi Sir

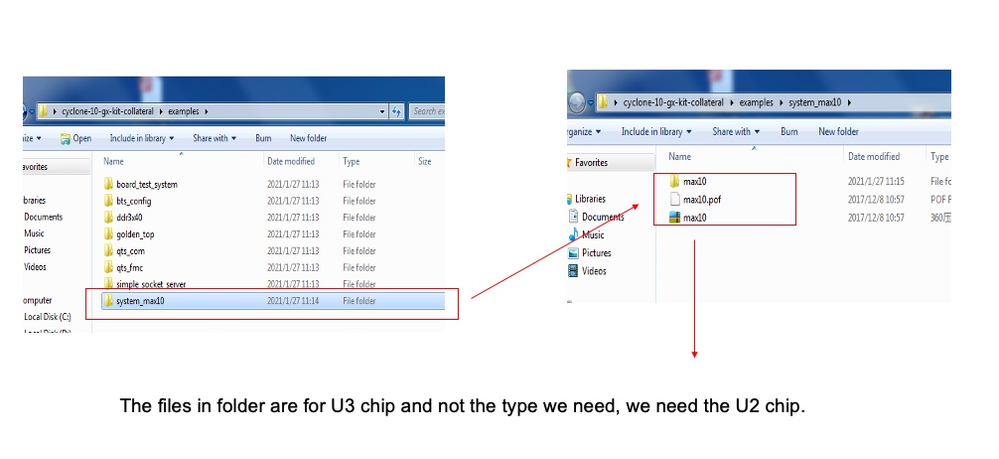

I got in to the link you provided, but the files are not the one I need, This files is for U3 chip(CFG MAX10), I need the files for U2 chip (SYS MAX10).

Could you please help to check again and provide the new link to me?

Thanks.

Hello,

Thanks for update. FYI, the board team stop providing the source file, we no longer provide the source code U2 chip (Intel MAX 10 FPGA Power Manager) file of system for any Intel Development Kit board. Apologize for any inconvenience caused. For pin configuration you can check in schematic diagram and board layout pcb Cadence .OLB file. Please find package here https://www.intel.com/content/www/us/en/programmable/support/support-resources/download/board-layout-test/pcb/pcb-cadence.html?elq_cid=4171900&erpm_id=2892549

You can provide me *.sof or *.pof file for the U2 chip. I am developing hardware use the chip Cyclone10GX base designed of Cyclone® 10 GX Development kit. Thank you so much!

Thank AabdRahman for the reply! Are you sure this is a file for U2 (SYS MAX 10) in Cyclone 10GX deverlopment kit?

We have not heard from you and I hope all is well. I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

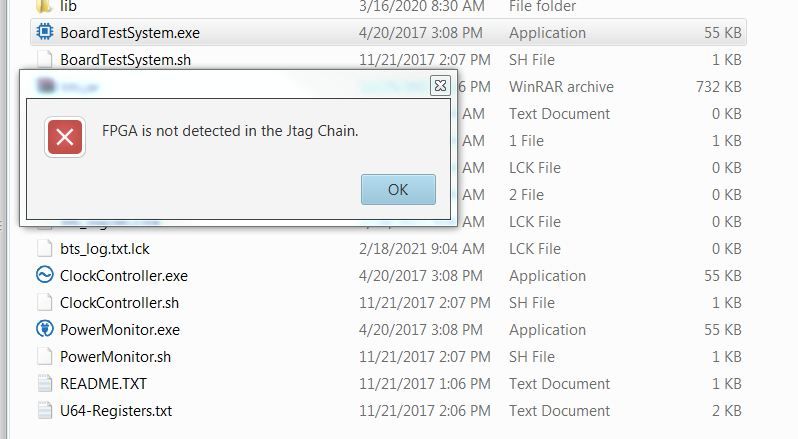

Thank AabdRahman! I am testing a new kit DK-DEV-10CX220-A but when I use BoardTestSystem. It can not start with the error "FPGA is not detected in the Jtag Chain"