- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel Support/Expert

I have a project with 16 lanes of JESD, before I integrate PCIe, it could be compiled successfully.

after I added in PCIe( Avalon-MM with DMA, Gen3X8, Interface:256bit, 250MHz). it failed while fitting,

Error(14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 HSSI_PMA_TX_BUF(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error(175001): The Fitter cannot place 1 HSSI_PMA_TX_BUF, which is within Intel Arria 10/Cyclone 10 Hard IP for PCI Express jesd204b_pcie_a10_hip_0_altera_pcie_a10_hip_2011_ubtnd7a.

Error(16234): No legal location could be found out of 72 considered location(s). Reasons why each location could not be used are summarized below:

Error(175006): There is no routing connectivity between the HSSI_PMA_TX_BUF and destination HSSI_RX_PCS_PMA_INTERFACE

Error(175022): The HSSI_PMA_TX_BUF could not be placed in any location to satisfy its connectivity requirements

Error(20196): Location(s) already occupied and the components cannot be merged. (8 locations affected)

I hope the chip has enough resources to hold both modules. I don't know how to manipulate the design to make the fitting pass.

Is there general procedure to tracing this kind of "no routing connectivity"?

I can provide the design if anyone want have a look.

thank you very much.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

KDB means Knowledge Base, It is the link provided by you

- Error (175001): The Fitter cannot place 1 HSSI_PMA_TX_CGB, which is... (intel.com)

- As mention it is more related to Native PHY IP (tranceiver), which might not be the error to your problem as you are using standard PCIe design.

Step how to Assigning Pin I/O Standards in the Intel® Quartus® Prime Pin Planner you may refer to the link.

For the correct Pin number, you may refer to the user guide below under Table 5-16 , page 72/103

Hope this is helpful, let me know if further clarification is needed.

Regards,

Wincent_Intel

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Thanks for reaching. there is an same error reported before.

For Error 14566 , you can try use the following assignment. set_global_assignment -name AUTO_RESERVE_CLKUSR_FOR_CALIBRATION OFF

Detail information you may get in the KDB https://www.intel.com/content/www/us/en/support/programmable/articles/000074695.html#:~:text=%C2%AE%2010%20devices%3A-,Error%20(14566)%3A%20The%20Fitter%20cannot%20place%201%20periphery%20component,and%20then%20rerun%20the%20Fitter.

Please try it and let me know the finding,

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent

Thank you for your prompt response, I tried it, it didn't work.

I searched the error database; I found this link is the closest one

Error (175001): The Fitter cannot place 1 HSSI_PMA_TX_CGB, which is... (intel.com)

You may see this error when using the Arria® 10 device, Native PHY IP in PIPE mode. This is error is due to a mismatch between bonding master setting and physical transceiver channel placement.

To fix this problem modify the bonding master setting in Native PHY IP to match transceiver channel placement. The bonding master should be in physical channel CH1 or CH4. For example, if the following x4 PIPE transceiver channel placement is used, the bonding master is 1.

| Logical Channel |

Physical Channel |

| Ch0 | GXBL1C_RX_CH3 |

| Ch1 | GXBL1C_RX_CH4 |

| Ch2 | GXBL1C_RX_CH5 |

| Ch3 | GXBL1D_RX_CH0 |

but I don't fully understand what the Description and Resolution is talking about.

could you please give me more detail of the resolution. I am not very familiar with PCIe IP, I instruction how to operate.

Thank you again.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

The KDB provided is for Tranceiver PHY IP (Native PHY IP) , not so related to PCIe. Not sure if you had include it in your design or not.

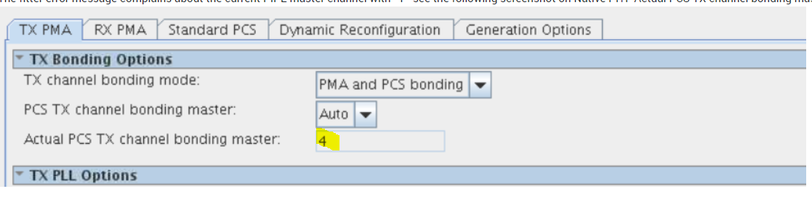

If have, you can set it as below picture, via the PHY IP GUI.

Each of our HardIPs has a dedicated perstn pin location.

PCIe IP need to assign to fix channel location, detail about the IP location you may refer to Arria 10 User Guide)

Please check and ensure that you assign correctly.

Hope this is helpful.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

What is KDB stand for? how to include it in my design?

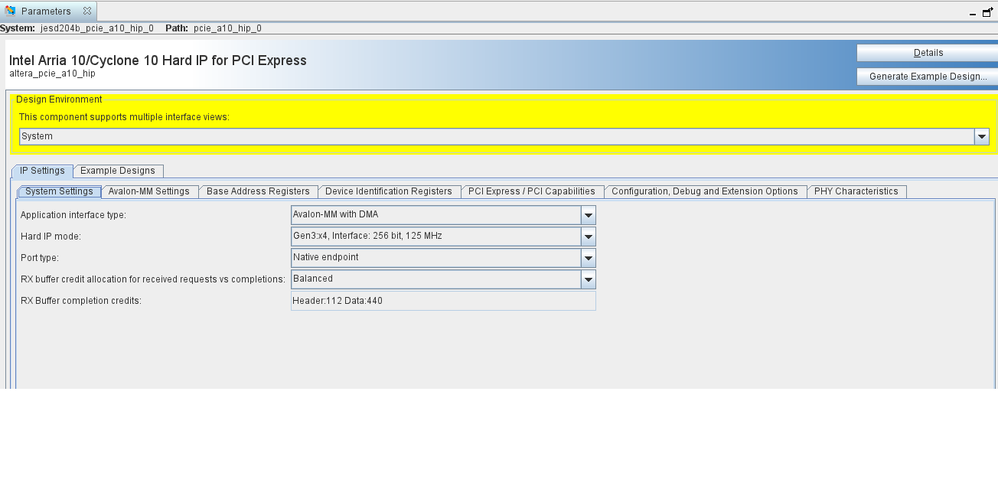

I am using standard Intel PCIe IP, here is the parameter setup interface. I couldn't see where I can setup bonding master.

I choose the parameters and generate example first, it compiled without any problem, after I intergrate to my design, the error happens. I guess there may be a resource conflict. so the assignment is the key point to solve the problem.

I also attached the QSF file of the example, it doesn't help if I copied all lines into my final project qsf file.

while I am checking how to assign the channel location. could you please give me a example of the .qsf with the channel location lock. it will make my learning process faster.

I am an old engineer, still need to learn new skill. Appreciate your help and patience.

Happy holiday.

.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

KDB means Knowledge Base, It is the link provided by you

- Error (175001): The Fitter cannot place 1 HSSI_PMA_TX_CGB, which is... (intel.com)

- As mention it is more related to Native PHY IP (tranceiver), which might not be the error to your problem as you are using standard PCIe design.

Step how to Assigning Pin I/O Standards in the Intel® Quartus® Prime Pin Planner you may refer to the link.

For the correct Pin number, you may refer to the user guide below under Table 5-16 , page 72/103

Hope this is helpful, let me know if further clarification is needed.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

After I made some correction following the user Guide, not it works, thank you very much.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Is there any new error message ? after the assigned ?

If yes appreciate if you can share with me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi wchiah

I guess the problem was because a typo of the highspeed pin name. after I corrected it, there is no error message anymore.

thank you for all the support

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Glad that your problem solve, Nice to work with you.

Feel free to create a new case if you face any problems in future.

If the case is assigned to me again, I am happy to continue working with you.

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or please let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent

most of the support request is due to the user don't know how to use the tools or device. sometime the requester just don't know where to get the data sheet or the user manual. if you give me a hint where to search for the answer will be 10. if you can tell me which section or your understanding. that will 10+.

thank you,

David

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page