- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

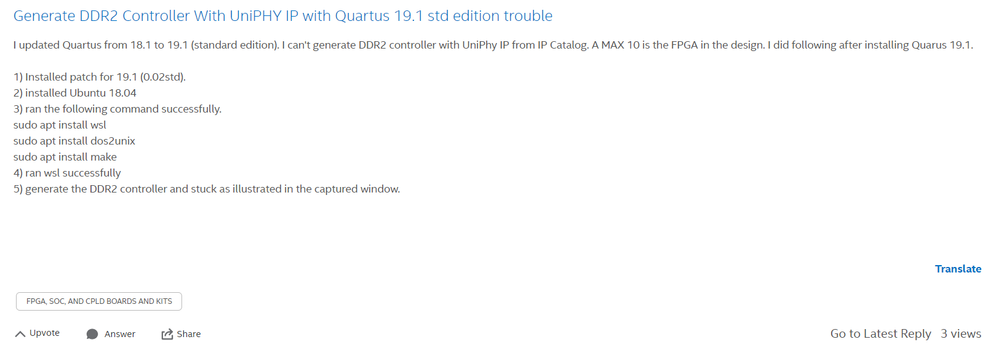

I updated Quartus from 18.1 to 19.1 (standard edition). I can't generate DDR2 controller with UniPhy IP from IP Catalog. A MAX 10 is the FPGA in the design. I did following after installing Quarus 19.1.

1) Installed patch for 19.1 (0.02std).

2) installed Ubuntu 18.04

3) ran the following command successfully.

sudo apt install wsl

sudo apt install dos2unix

sudo apt install make

4) ran wsl successfully

5) generate the DDR2 controller and stuck as illustrated in the captured window.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @TLu4 ,

Welcome to Intel Community.

Are you attached some document/picture? I am sorry but I am not able to view any captured window as you mentioned (see below). Can you please help to re-send?

Thanks

Regards,

Aida

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

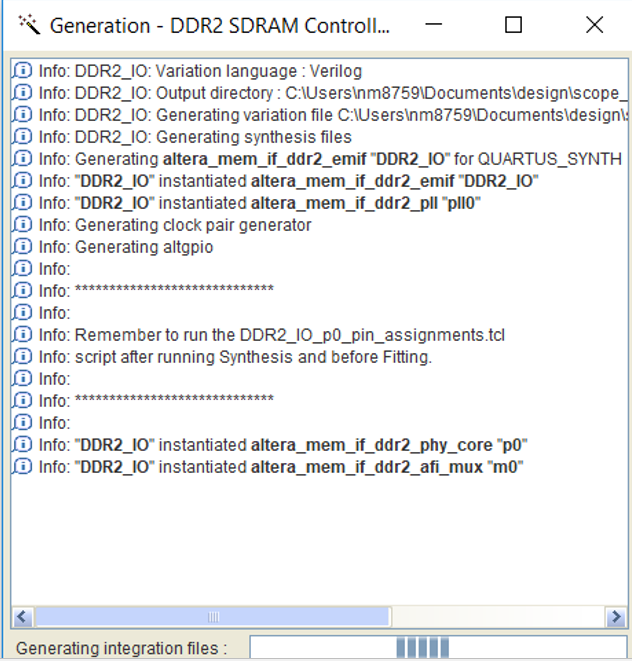

Hi Sir,

I am able to successfully generate the IP.

You may refer to this KDB which is related to WSL usage. --> https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/tools/2019/how-do-i-install-the-windows--subsystem-for-linux---wsl--on-wind.html

You may check on your OS version whereby the recommended OS would be Windows* 10 build version 16215.0 or higher. Also make sure to follow standard instructions from Microsoft® to install Ubuntu* 18.04. The link on the guideline provided in KDB above.

Hope this helps.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page