- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using high speed ADC (ADS62P25IRGCT) with arria10,

Output of ADC is LVDS, i want single ended input in FPGA,

GPIO ip: is Not suitable as specified in datasheet.

GPIO Intel FPGA IP User Guide: Intel Arria 10 and Intel Cyclone 10 GX Devices

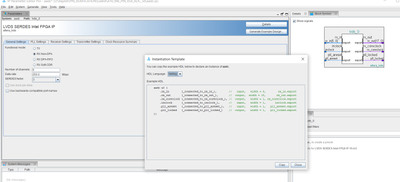

2)LVDS serdes IP:

LVDS SERDES Intel FPGA IP User Guide: Intel Arria 10 and Intel Cyclone 10 GX Devices

The output is parallel and width is multiple of SERDES Factor.

These two may nit suitable for my requirement,

please suggest IP for LVDS to single ended input in FPGA.

Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

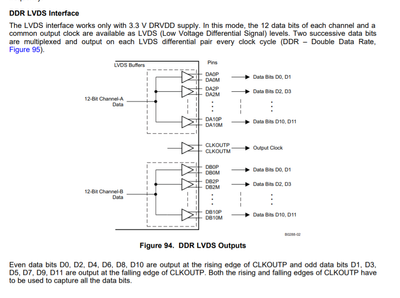

Yes, you can use it to convert the differential signal to single ended and implement the DDR data capture logic to it. The IP basically configures the IOE element of the device.

Regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

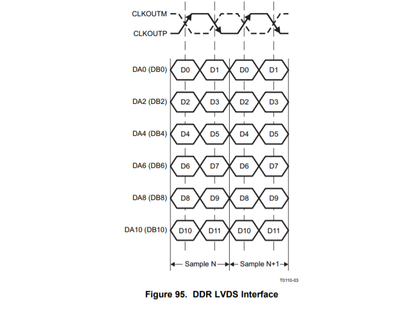

ADC is DDR LVDS output,

Please suggest IP which features LVDS and DDR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The GPIO Intel FPGA IP can be configured to be used with a differential buffer and DDIO as Register mode. You can assign LVDS IO standard to the input pin.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Ash_R_Intel ,

Thank you for response.

from the GPIO IP Datasheet : "You can use GPIOs in general applications that are not specific to

transceivers, memory interfaces, or LVDS."

by the statement given in datasheet,

can we still use GPIO IP for LVDS pins ?

Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, you can use it to convert the differential signal to single ended and implement the DDR data capture logic to it. The IP basically configures the IOE element of the device.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page