- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I download EP4SE530's IBIS model, but I can not find the dedicated high speed clock input pins in the model. The pin name is CLK[1,3,8,10]. So how can I simulate dedicated high speed clock input pins in HyperLynx by FPGA's IBIS model?

Yours,

Longyu

1 Solution

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fang Longyu,

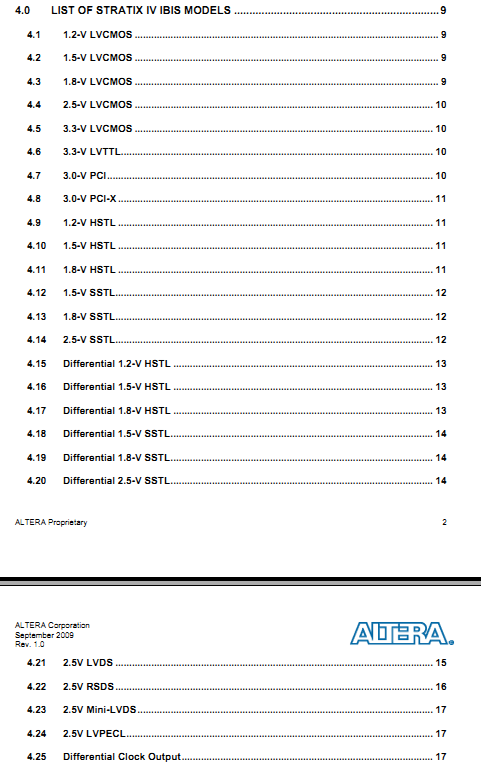

There is no dedicated IBIS model for these pin. Since the I/O Standard in Intel PSG FPGA is programmable, you may use the I/O standard that you choose for that input clock pin as the IBIS model. Example: if you use 2.5V I/O standard, you can use 2.5Vcmos IBIS model.

Regards,

YL

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fang Longyu,

There is no dedicated IBIS model for these pin. Since the I/O Standard in Intel PSG FPGA is programmable, you may use the I/O standard that you choose for that input clock pin as the IBIS model. Example: if you use 2.5V I/O standard, you can use 2.5Vcmos IBIS model.

Regards,

YL

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page