- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel Support,

In the process of debugging I2C communication using FPGA, I accidentally damaged the FPGA. Specifically, I saw the I2C SDA (PIN26) short-circuit directly to the ground, but the specific damage is not known for the time being.

In addition, the J1 PIN with a multimeter are tested to open SHORT circuit, found that PIN3(not used) is also SHORT to the ground.

Is there any solution to repair the FPGA?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sancy,

Good day!

May I know the what is the part number of the FPGA?

Wani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did I answer your question? Can you give some updates on this issue?What can I do next?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

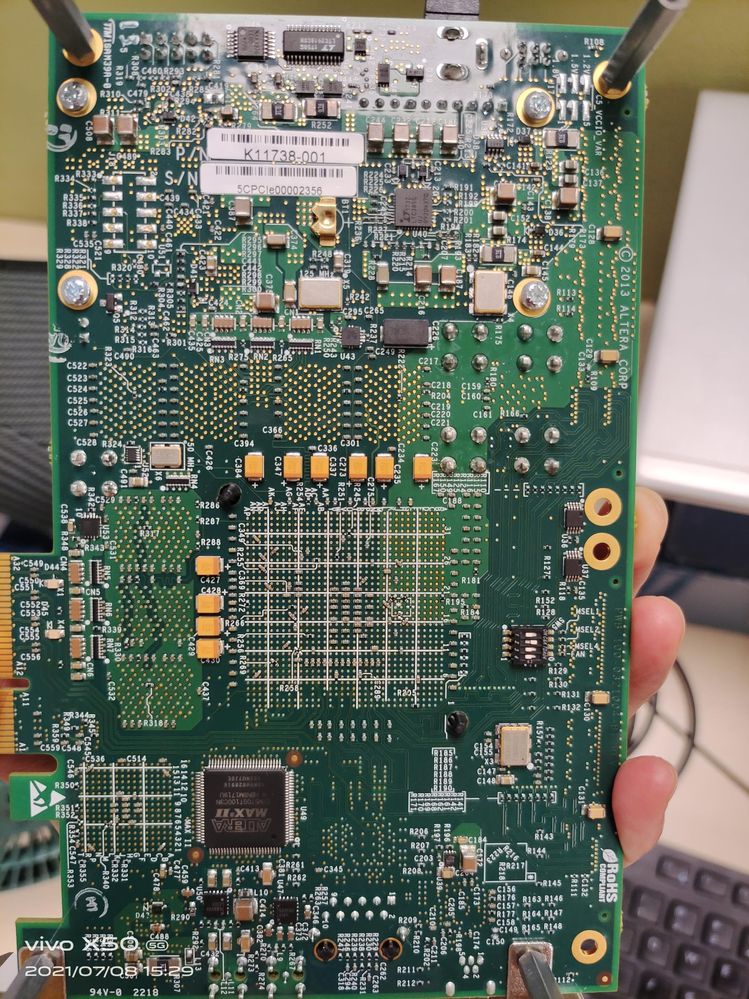

Oh I am so sorry for my late response. Can you share the photo of the device? I can check the part number from the marking. Or if you want to make it as confidential, I can start a private email. Please do let me know.

Thanks!

Regards,

Zawani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your quick reply. The following is the FPGA image. We need to make it as confidential. Thx.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The pin3 refers to the third pin in J1 area.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wani,

Thanks for your reply. For the FPGA image, I think we can keep it as public since I cannot reply to you via my work email because of the security IT policy.

For the Pin3 in J1, the name is HSM_D0. Actually I have returned two Cyclone-v GT FPGA platforms to Intel for RMA service previously, even though the communication and maintenance period is a little long, we got a statisfied result finally. For this damaged FPGA, we suspected it is not a very serious problem, we want to know if it is possible that Intel can provide us guidance to repair it by ourselves by replacing or removing some electronic devices or component.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sancy,

FPGA is a sensitive device. Once the device is damage (in this case it is shorted to GND/open) it cannot be repaired.

It is advised to handle the FPGA in allowable operations specs and static-free environment to avoid electrical damage.

You may refer to PSG Data Book and the application notes as reference.

Wani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Wani,

Is it possible that I returned the FPGA to Intel for double-confirm the issue?I am not sure whether it is Shorted to GND and cannot be repaired, it is just my prelinary adjugement. Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sancy,

Please be informed that EOS is not cover under warranty, any of the reasons caused by EOS event will not be approved for failure analysis support.

However, I like to understand more on your issue so we can get some picture on how it can be damage.

Can you tell me the story of this part :

1. How you found it is failed?

2. What kind of test have you done?

Thanks!

Wani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the process of debugging I2C communication using FPGA, my teammate saw the I2C SDA (PIN26) short-circuit directly to the ground, but the specific damage is not known for the time being.

In addition, the pins of J1 have been tested with a multimeter for SHORT circuit, and it is found that PIN3 (unused) in J1 area is also SHORT to the ground.

Am I going to lost this FPGA according to your statement, EOS event will not be approved for failure analysis support from Intel. A little regreatful and sad. But anyway, thanks for your time and support.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page