- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Intel Stratix 10 GX FPGA Development Kit L-Tile

1SG280LU2F50E2VG / 1SG280LU3F50E3VGS1 (User guide is not clear)

I have configured a ROM to "Allow In-System Memory Content Editor to capture and update content independently of the system clock" with 'instance ID' of this RAM set to 0001.

Once synthesized, I am able to program the Stratix 10 on the development board and connect to the ROM using the In-System Memory Content Editor.

When I read data from the ROM, the tool reads the same data for all addresses.

Attempts with other memories in the design have the same problem.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The obvious question is: is this how you initialized the ROM? Assuming the answer is no, then you have to look at how you're initializing the ROM: .mif, .hex, and are you using an IP and set the parameter to use the appropriate file or the ram_init_file synthesis attribute for an inferred ROM?

For your memory initialization file, can you open it in Quartus and confirm that the correct data is in that file?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The .mif file is correctly loaded. Once synthesized the contents are readable and have been verified.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@DaveMM wrote:The .mif file is correctly loaded. Once synthesized the contents are readable and have been verified.

So does that mean you've solved the issue? Or are you saying that the ISMCE is not matching what you are seeing in the functional design?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I was not clear. The In-System Memory content editor does not work. Reading the memory from our design interface shows the correct memory content. Our system is working and running code from the ROM. We would like to use the In-System Memory content editor to allow our SW team to make modifications.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's very strange. Are you sure you're looking at the correct ROM in the ISMCE? There's been a bug where the ID always displayed "NONE" even if you set an ID in the parameter editor (though your screenshot does show that you've named this one "TROM").

Have you enabled the continuous read option in the ISMCE? The contents in your screenshot are all colored red, indicating that you did a one-time read and these might not be the current contents.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The ROM I am trying to read/write with the ISMCE is the only instance of this ROM.

I have tried continuous read, read selected words, and just about every combination I can think of.

Reading the contents a second time does change the red to black, but the data does not change.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is the data at least correct for the first set of address locations and then the repeated data is incorrect?

It's a long shot but you could try reducing the JTAG frequency (you can go down to 6 MHz) to rule out if this is a JTAG issue.

Related to that, there is a template in the Quartus text editor to add timing constraints for the JTAG interface to your .sdc file. Might want to check that out.

And is your design meeting timing? It could be on the edge, which would explain it working OK functionally but having some issues like this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The data read out does not match any of the preloaded data at any address.

Whatever it reads out the first time it persistently sticks with.

Timing constraints are met.

I will add the JTAG timing constraints to my SDC file. (Currently using the Quartus default)

Are there any special timing constraint considerations on the JTAG interface when using the Stratix 10 Dev board?

Just some additional information: The ROM is defined with no output data registering. (Not my design, I'm just the emulation droid)

I will give the reduced JTAG frequency a try as well if the change to constraints does not work.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

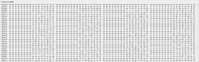

I'm using RAM to get the data stored in the ROM and able to get every data being recorded in ISMCE check the screenshot below. Instance 0 is ROM while Instance 1 is RAM.

Attached the .hex (WIDTH=8; DEPTH=64;) and .sdc files for your reference. Could you try with the attached .hex file format and see any different? Btw, JTAG frequency is 16Mhz.

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @DaveMM ,

Do you have any further update or concern on previous post link community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/In-System-Memory-Content-Editor/m-p/1525399#M25875?

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I've been having difficulty with the Intel support "single user sign-on error" (Still having problems)

Anyway, I've tried your suggestions (JTAG SDC / Lower JTAG frequency), but I am still stuck in the same spot.

I did finally find a location in my ROM that corresponds to the data I am seeing on the viewer.

The ISMCE is reading data from one address and this data is displayed for all addresses.

Even if I ask to read only address 0, I get the data from the one address it is stuck on.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Possible provide your .hex or .mif file for testing?

Thanks,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, the contents are proprietary.

I know the contents are getting loaded. The code executes correctly.

The dimensions of the ROM are, width = 128, depth = 4096.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi DaveMM,

Any further concern on the previous post link community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/In-System-Memory-Content-Editor/m-p/1528525#M25953

Thanks,

Best Regards,

Sheng

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page