- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

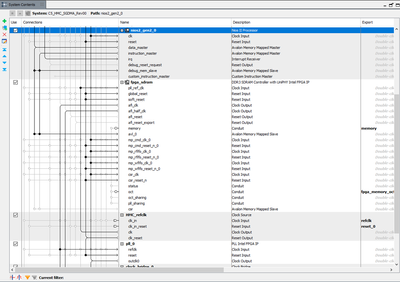

Hope all well and I appreciate if you take a look at this and see if you can help us. We are using Cyclone V GT Dev board to test DDR3 HMC controller. We used 32 bit SGDMA to write into DDR3 and used NIOS II to read back from every available address to confirm the data. it is working fine with no issues. NIOS II code running on on-chip memory.

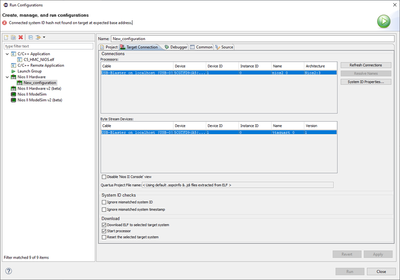

Then we removed on-chip memory and tried running simple hello world. I should also confirm that SGDMAs removed from design to simplify the design. however, when we are trying to start the NIOS, the error message pops out saying “Connected system ID hash not found on target at expected base address.” I know when this happens , there might be something wrong with system. However, we are yet unable to find the issue.

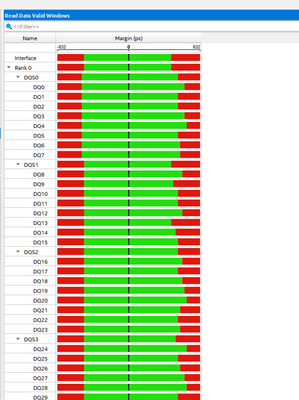

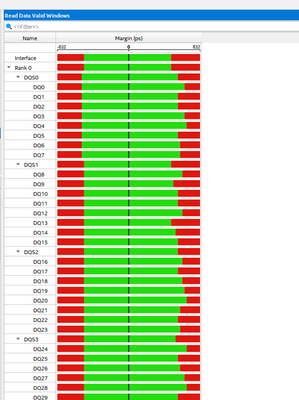

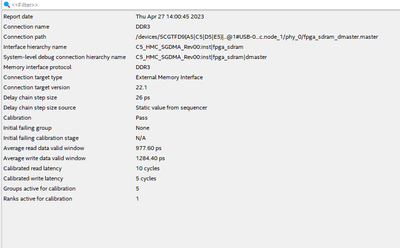

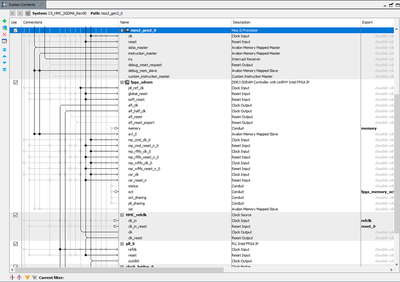

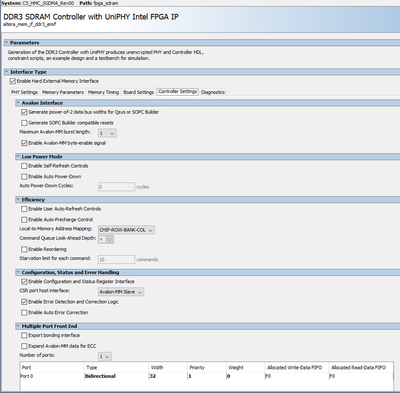

I should say that HMC core passes the calibration margins. Please see attached. DDR3 using single 32 bit bidirectional port avl_0 and both NIOS data master and instruction master connected to it. exception and reset vectors correctly set and NIOS alongside other peripherals running at 50MHz. any help appreciated. I should also mention that, when we change the ip core to soft memory controller system works fine.

Looking forward to your valuable comments. Some pictures below

Regards,

Aidin.

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aidin,

Sure no problem. At the mean time I will dig around and let you know as soon as I have any findings.

Thank you.

Best,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Excellent.

Thanks Kelly

Regards,

Aidin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I think I may have found the root cause to why it passes the Soft memory controller and not HMC:

Thanks.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kelly,

can you please elaborate your note? what do you mean?

Regards,

Aidin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kelly,

Thanks for your email. we have always used DDR3A for our application. These are the cases we have tried

1. 40 bit HMC implemented on DDR3A with 32 bit bidi Port and Nios II was unbale to boot up (DDR3A was functional - confirmed by SGDMA data pattern) frequency range from 302 MHZ to 400 MHZ tried

2. 32 bit HMC implemented on DDR3A with 32 bit bidi port and Nios II was unbale to boot up(DDR3A was functional - confirmed by SGDMA data pattern) frequency range from 302 MHZ to 400 MHZ tried

3. Soft memory controller implemented on DDR3A (40 bit) with 302 MHz and Nios II was working fine (256MB DDR3A)

4. Soft memory controller implemented on DDR3A (32 bit) with 302 MHz and Nios II was working fine (256MB DDR3A)

5. Reduced the accisable memory size to 32 MB using HMC and Nios was not working. Soft Controller with same memory size is functional.

During our tests , we have always used DDR3A and never tried DDR3B. I can see regarding instruction master to be 28 bit wide so why it works with soft memory controller but not HMC?

Regards,

Aidin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Unfortunately, This Nios® II processor instruction master cannot address more than a 256 MByte span of memory; consequently, providing more than 256 MBytes to run Nios® II software wastes memory resources and causes system ID not found on target at expected base address.

I hope this answers your doubts.

Thank you.

Best,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Kelly,

something is not adding up here . data sheet says 256MB however, Nios and Platform designer see the memory size of 512MB? could this be a problem? see below from platform designer?

Thanks

Aidin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aidin,

So is everything all good? Is there any further support needed from my end?

Thanks.

Best,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kelly,

one last thing: as I mentioned, on CV GT Reference manual states DDR3A is 256MB. However, Nios and platform designer see the Memory size of 512MB? am I missing a point? All row and Column address are correct from data sheet.

Regards,

Aidin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aidin,

The NIOS II on platform designer should be no issue as you have all your project settings done.

The only down side and limitation is HMC does not support NIOS II with large memory bytes, and soft memory controller is able to support larger memory.

Are you able to proceed with Soft Memory Controller for your project and are you happy with the workaround?

Hope to hear from you.

Thank you.

Best,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Kelly

I think HMC is not supporting NIOS in any size of memory as we have tried various sizes. Hopefully, this will be updated in future to make things easier.

for Now, we will create a on chip memory to work with and if needed will use soft memory

Thanks for help

Regards,

Aidin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

Thank you.

Regards,

Kelly Jialin, GOH

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »