- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

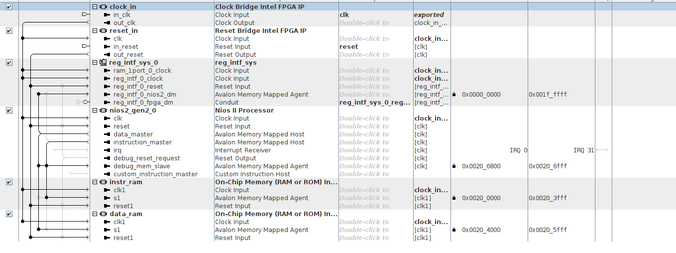

I am trying to understand the address mapping for the data master in the NiosII processor. Currently, I have a system that looks like this:

The nios2 data master is connected to two slaves - a "data_ram" which I want to be used for all data related transactions, the debug interface "debug_mem_slave", and "reg_intf_sys_0" which is a peripheral register I want to access from the NIOSII.

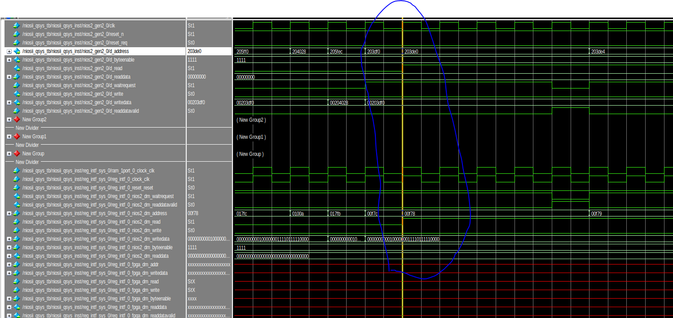

Now the strange part is that the address mapping seems to indicate only addresses from 0x0 -> 0x1f_ffff are supposed to go to the "reg_intf_sys_0" but when I ran a simulation I see this:

I can see the d_address (the data master address) performing a read at address 0x203de0, but it seems to be accessing the reg_intf_sys_0. I'm just a bit confused about why it's accessing this address space. I don't have any code on the NIOS2 that accesses this region, I have attached the "hello.c" file that I am running on the NIOS2. The address mapping seems strange, so I wanted to ask about it.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you connect the data and instruction bus of Nios to an on-chip RAM.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page