- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am looking at methods to write/read from DDR from my host system through the PCIe Hard IP block.

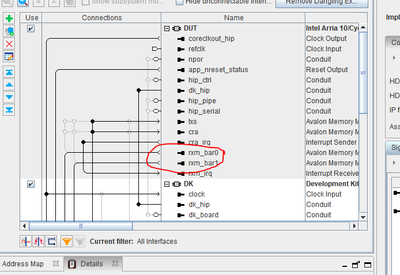

I have looked at some examples for Qsys projects using the PCIe Hard IP block and I understand how the rxm_bar<n> Avalon interfaces are used to access memory mapped regions through PCIe:

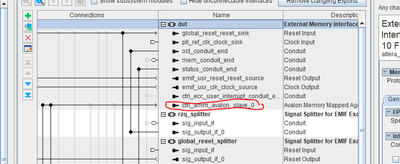

I also saw an example of the "External Memory Interface IP" to see how to communicate to DDR and I see the Avalon Slave on the EMIF is used to read/write to DDR:

However, I cannot connect the rxm_bar<n> interface directly to this because the EMIF provides its own clock for the transactions to the EMIF.

I guess I can add a dual port Avalon-MM in between both of these (so the PCIe Hard Macro writes to the Avalon-MM memory and perhaps a DMA reads data from this BRAM and pushes it to the EMIF) but I was not sure if there was a more elegant way of doing this. I think others must have done something similar to this, so I wanted to ask if there was another way.

Thanks!

Prateek

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can find Intel FPGA PCIe reference design that interact with either DDR3 or DDR4 memory in below link. Feel free to check it out

Goto the left panel -> click on "user guides and reference designs" -> click on "reference designs" tab

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi,

I looked at the guides and it refers to using an "Avalon-MM DMA" type interface for the PCIe when communicating from PCIe to DDR. I'm looking for something that is only an "Avalon-MM" interface. Is there a reference design that perhaps deals with only "Avalon-MM" interfaces?

I am also trying to download the "Arria 10 Reference Design" link on page 3 from this PDF: PCI Express DMA Reference Design Using External Memory (intel.com)

However, I get a "File Not Found" error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

The AN708 was older ref design doc that pointed to old outdated Altera ref design link that doesn't exist in Intel system anymore.

If you are looking for A10 PCIe example design, you can generate the example design directly from PCIe IP. Check out below link

- https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-dex-a10-pcie-avmm.pdf

- This example design is targeting FPGA on chip memory but you can replace it with DDR3 or DDR4.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi,

How can I go about replacing it with DDR3 or DDR4? I believe the only way is to use the IP Block "External Memory Interface IP" right?

The problem with this IP is that it provides its own clock reference to the master that is writing/reading to it. However, the PCIe Avalon Master is running off the PCIe clock (250 MHz). So how would I replace the BRAM with a DDR3 or DDR4?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am still wondering about this - can someone let me know if I am thinking incorrectly about how to make PCIe write to DDR? It seems odd that a direct connection is not feasible so that's why I wanted to check.

Prateek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Pls see my reply below.

- Yes, you need to initiate external memory interface IP to use DDR3 or DDR4

- For the different clock frequency connection issue between PCIe Avalon MM Bar and DDR3 Avalon MM interface - I think you can use "Avalon MM clock crossing bridge" IP in platform designer to handle the different clock domain crossing

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page