- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello support team,

We are planning to use Intel Agilex series FPGA: AGFB027R24C2I3E along with the external analog devices multiple ADC device ( AD9653).

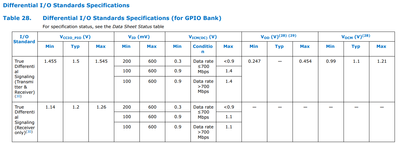

As analog devices ADC device is providing digital outputs and clocks in LVDS having 1.8 V IO standard which I need to interface to Intel agilex series FPGA GPIO Banks ( total 192 LVDS IOs for 12 Nos of AD9653 and total 48 LVDS output clocks). Which GPIO Bank would be suitable for this as in the GPIO user guide, I have not found any 1.8 V compatible GPIO Banks. Request you to provide guidance for the same.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Maitry,

You can refer to the following two Knowledge Database Articles.

As long as the common mode range and the differential voltage swing is compatible between the two devices there will be no problem and you can DC couple the interface.

https://www.intel.com/content/www/us/en/support/programmable/articles/000078537.html

https://www.intel.com/content/www/us/en/support/programmable/articles/000074485.html

Check the I/O standard specifications of the ADC device you are using and see if VOD, VOCM of ADC LVDS output falls in the range of Agilex 7 VID and VICM. The same when checking Agilex 7 output to ADC input.

Thanks & Regards,

Xiaoyan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martry,

I wonder if my answer resolved your question?

Thanks & Regards,

Xiaoyan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Xiaoyan,

Thank you for your response. Yes, I got your point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have gone through the ADC datasheet, in which my LVDS output offset voltage( VOS) range is 1.15 to 1.35 V. So, in order to fall the ADC output range in intel agilex series FPGA GPIO bank IO standard, I need to use the GPIO Bank VCCIO_PIO at 1.5 V, right?

I have checked in the reference schematic, in which by default GPIO Bank is operating with VCCIO_PIO at 1.2 V. In order to provide VCCIO_PIO at 1.5 V , Is there any software configuration need to operate these GPIO bank with VCCIO_PIO at 1.5 V?

Awaited your response.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page