- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

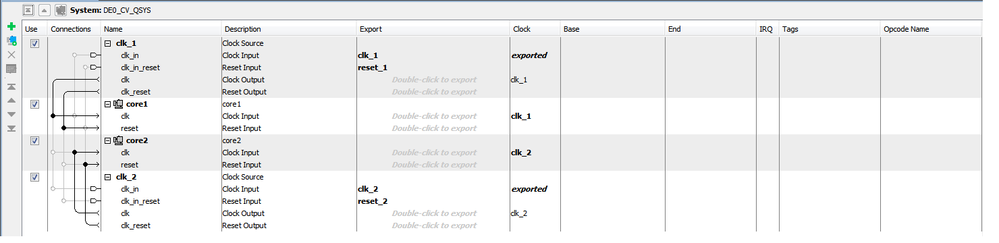

I am working on DE0-CV board. I am trying to share SDRAM by two NIOS cores. They don't need to share data, basically they just need to partition the SDRAM and run two different applications that I can't fit on onchip memory. My current top design is :

I don't know I can add a shared memory controller in this design. I tried to add a controller in each core and connect each of them to SDRAM inputs but apparently that doesn't work(only one controller can be connected to input). If I need to connect both of them to one controller, I don't know how to connect core1.datamaster to onchip memory, etc. and also export to connect to the shared controller in higher level. I would appreciate if someone can help me with this. I am attaching my current design.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

DE0 board only contains 1 SDRAM memory device interface. Therefore, you can't create 2 SDRAM IP in QSYS.

It would be easier to hook up everything under same QSYS interface rather than create sub-block design (core1, core2) to verify the design connection first. It's easier to manage to QSYS addressing as well.

For instance, using core1 sub-block design. I tried out following combination

- 1 NIOS to connect to both on chip RAM and SDRAM (ok, no error)

- 2 NIOS to connect to same on chip RAM (ok, no error)

You can read more about QSYS usage guideline in below link as well

- https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qps-platform-designer.pdf

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page