- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For a particular design I have an external, 1 GHz, clock. An ideal solution would be to use this clock to clock some FPGA logic. I aim to use a 1:1 PLL clock to help improve timing and clock routing within the FPGA fabric.

The issue I'm running into is finding the maximum IO toggle frequency for Startix 10 FPGAs. I am aware that the maximum I/O toggle frequency is greatly affected by the input standard used (LVTTL 3.3V,2.5V etc). However I would expect to see some characterized values on a datasheet somewhere, but that I am yet to find.

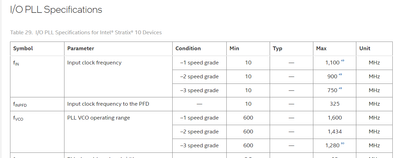

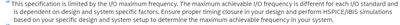

I have found this table in the Startix 10 datasheet which describes the PLL clock maximum input frequencies. However it is un-clear to me whether this table is describing the maximum input frequency from a physical, dedicated, I/O pin/pad or from internal routing along clock nets in the FPGA fabric.

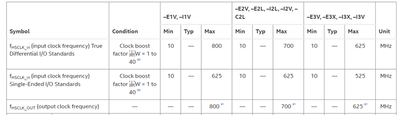

There is a periphery section of the datasheet which may elude to what I'm after. Here it shows that the Highspeed I/O Specifications. For single-ended standards, the maximum frequency is 625MHz. However from how this section reads, I am unsure if this applies to the dedicated clock pins/pads on the FPGA.

The information I'm after should be present in Quartus Prime Pro, however I feel this information should be available before I've made the platform investment in a Pro license.

If anyone can point me in the right direction that would be appreciated.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for reaching out Intel FPGA Community.

According to this Knowledge Base article, refer here Will Altera publish the maximum I/O toggle rate specifications for... (intel.com), unfortunately we are not published the maximum IO toggle frequency in the datasheet for newer device anymore.

All of the standard supported I/O signaling frequencies is depended on design and also system customization form factors.

Therefore, the I/O toggle rate specifications was being removed from Stratix 10 device datasheet. The best options are using HSPICE or IBIS simulations.

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided, please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page