- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am using a Stratix 10 TX board.

I want to use its transceiver to drive the SMA cables, but I have no experience with this kind of transceivers and any help is indeed appreciated.

I am using this design as reference:

Testing the design with the Transceiver Toolkit, the loopback with an SMA cable and with PRBS test pattern seems to work.

However, I would like to send some custom pattern with the TX SMA channels and I see that in the Transceiver Toolkit there is this "USER" options:

I then saw on the "E-Tile Transceiver PHY User Guide" that it is indeed possible to send User-defined 80-bit Pattern.

But it is not clear to me how I can do that. Looks like there are some PMA registers to write but I am not sure, and I did not understand how to do that.

Could somebody give me some help with this ?

Thank you in advance,

Enrico

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is a 'Data Pattern Generator' block within the E-tile PMA. You choose it to send user-defined data.

Refer for the description: https://www.intel.com/content/www/us/en/docs/programmable/683723/current/data-pattern-generation.html

For related registers and example refer below links:

https://www.intel.com/content/www/us/en/docs/programmable/683723/current/prbs-usage-model.html

You may also want to instantiate the Avalon-St Data pattern verifier block (available in IP Catalog) for validation of received data.

Recommend you to go through XCVR toolkit training video for usage in general.

https://www.youtube.com/watch?v=bwhyJuphy8I

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks a lot for the answer.

It is still not clear not me how to access these PMA registers. For example, in the E-Tile PHY User Guide there is this example that you provided (https://www.intel.com/content/www/us/en/docs/programmable/683723/current/user-defined-pattern-example.html ).It is clear to me that I have to operate the steps listed there, but I don't know how to do that.

For example, let's take the first row:

"Write 0x84[7:0] = 0x03"

I guess it means that I have to write the value "0x03" in the byte at the address "0x84"? But how do I assess this command? I really don't understand and I think I am missing something here.

Regards,

Enrico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

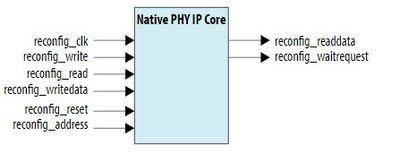

Check section 7 of E-Tile Transceiver PHY User Guide (links in previous comment).

Section 7.3, Figure 98 shows the ports when you enable this feature.

Further sections 7.5 and 7.6 provide timing details on how to access these ports.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ash,

thanks for the answer. It helped me clarified my ideas.

However there is still something that bugs me

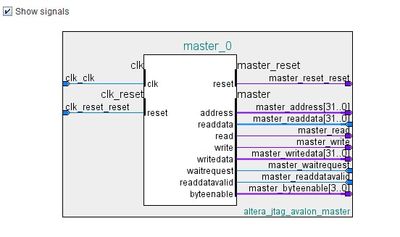

I see that in the example design that I am using is included (but not used! it is leave unconnected) this IP core "JTAG to Avalon Master Bridge Intel FPGA IP":

And its signal matches with the ones of the E-Tile Native PHY IP core, as in the Figure 98 that you mentioned:

Browsing on the online documentation, it looks to me that it is possible to use the "JTAG to Avalon Master Bridge Intel FPGA IP" to send some commands directly from the System Console and interacts with the design.

Let's suppose the I connect correctly this IP to the design (now, as I mentioned, is not connected): would it then be possible to access the transceiver PMA registers and program them from the System Console, instead of writing a custom logic (in VHDL/Verilog) to access these registers?

In other words: would it be possible to execute these instructions just by playing with the System Console?

Would you have maybe some design/examples/tutorials in that case? I see that in this thread the user @SyafieqS_Intel send to another user a zip file containing tutorial related to write and read avalon mm using jtag to avalon master bridge. In case I could have access to that, it could be highly beneficial for my project.

Regards,

Enrico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have sent you the files from other thread via e-mail. Please check.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ash,

Thanks for the file.

In the meanwhile, I figured it out by myself how to load the User Pattern: I leave some hints here in case it would be useful to somebody.

I used the some of the functions of the script "Ttk_helper_s10tx.tcl" that you can find together with other examples in this link . I managed to send the pattern through System Console commands using these functions.

I didn't have to connect the "JTAG to Avalon Master Bridge Intel FPGA IP" to the rest of the design.

Regards,

Enrico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Glad to know that. Closing the case. However, it will be open for community users to comment.

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page