- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

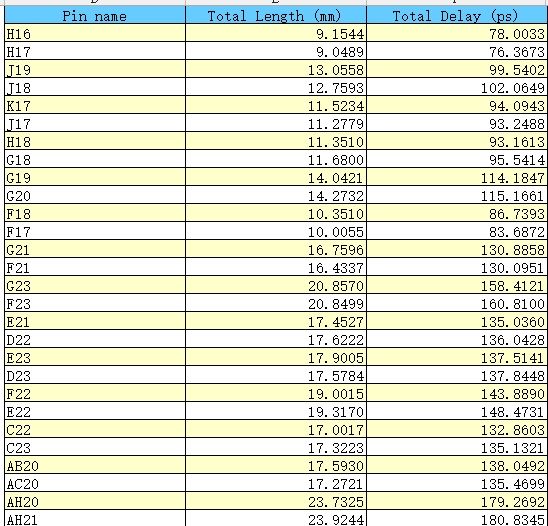

I downloaded this table(10AS032EF29_netlength.xlsx) from the official website, but there are two columns in it: Total Length (mm) and Total Delay (ps). Which data should I take as the criterion? What value should I set in the PIN DELAY of the PCB?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You may use Total delay(ps) as your pin delay setting.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Farabi

Thank you very much for your answer.

I still have questions:

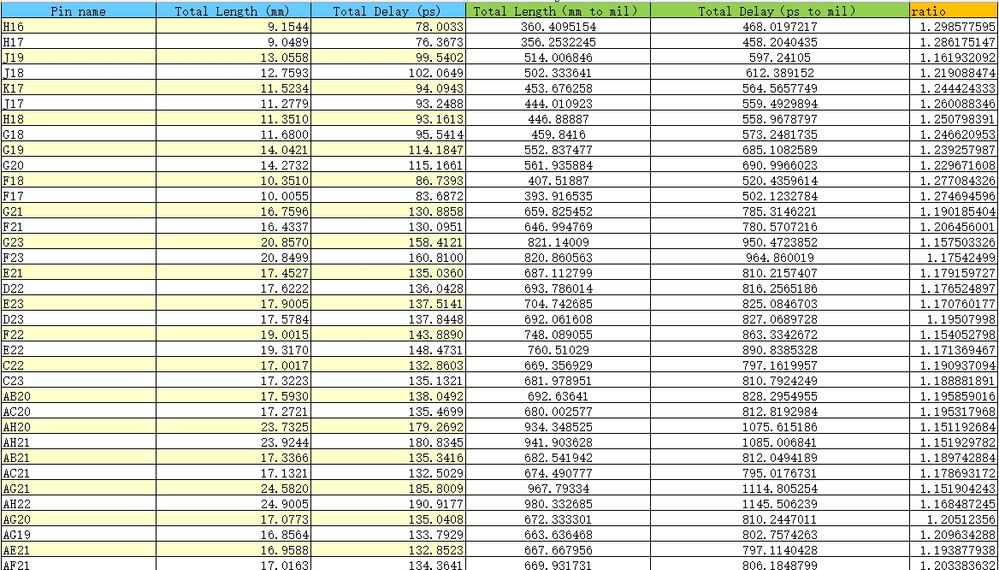

why is the the ratio of "total length(mm) "and "Total delay(ps) " different?It's supposed to be a fixed ratio。

or what is the difference of the "total length(mm) "and "Total delay(ps) "?

Best Wishes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

May I know why you think it supposed to be a fix ratio?

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

first, I think the ratio of length to time represents the rate, it's a constant value.

second,The purpose of equilength is isochronous. The length should equal the length of the delay.(1mm=39.72mil , in FR4 PCB, 1ps≈6mil )

If they're not equal, it's a proportional relationship. I don't know if I understand this right?

Regards,

gongmh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Okay, thank you for feedback.

I am consulting the internal team to get the confirmation on this matter. I will come back to you with the answer as soon as possible.

Thank you for your understanding.

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share the whole part number of the Arria 10 device that you used?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I got some input from the internal team on this question.

This design has been routed in strip line and microstrip line routing. These two have a difference speed between them. The speed in the microstrip line is faster compared to the strip line. Thats why the ratio is not fix.

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello ,

Do you mean that there are microstrip lines and strip lines inside the FPGA? So the two values are different?

My understanding is that the delay should be the same in FPGA inside, Because the routing is already established.

best wishes,

gongmh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided, please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

thanks for you help.Is there anyone who can answer my question?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page