- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have triple speed ethernet ip from collateral file of cyclone 10 gx. I want implement this xcvr block for sfp compatible. Which ip blocks should be added with this triple speed ethernet ip to make it compatible sfp xcvr.

I have taken ref. design example from cyclone 10 gx collateral simple_socket_server design example for triple speed ethernet & qts_pcie_sfp design example for sfp xcvr.

Please reply if someone have any idea regarding this query.

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I understand your question, you have instantiated the TSE IP core, and is asking which IP block is needed to interface the TSE IP to transceiver & SFP.

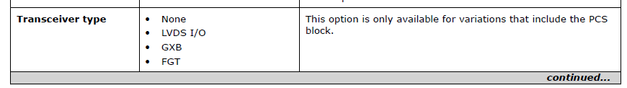

Once instantiated the TSE IP in the design, you just need to set the TSE IP GUI's 'Transceiver type' to 'GXB', then assigned the xcvr Tx/RX channels to the respective FPGA pins in Quartus design. Respective GXB module is included for target devices with GX transceivers.

Snapshot below showing the GXB option, from Cyclone 10 Triple Speed Ethernet IP Core User Guide, Table 18

https://www.intel.com/content/www/us/en/docs/programmable/683402/21-3-19-5-0/about-this-ip.html

The link below consists of more TSE User Guides and example designs for your reference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Yes i have taken the same approach. I have made an example with using TSE IP . Please find PDF file of design example & share your view.

Thanks for your reply.

https://drive.google.com/file/d/15RMoVfk7B6L_ZW7DwtMOSw33JLrcrYS5/view?usp=sharing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your block diagram consists of TSE core, transceiver native phy, PLL, transceiver reset controller, msgdma, it looks fine and is similar to one of the example available at below link.

Arria 10 - Triple-Speed Ethernet and Native PHY design example:

https://www.intel.com/content/www/us/en/design-example/715131/arria-10-triple-speed-ethernet-and-native-phy-design-example.html

Documentation User Guide:

https://www.intel.com/content/dam/altera-www/global/en_US/uploads/e/e0/Arria_10_Triple_Speed_Ethernet_and_Native_PHY_Design_Example_User_Guide.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thanks for your reply.

This design example is works on Arria 10 devices, we are working on cyclone 10 GX development board. So, do you think this design example is useful for cyclone 10 Gx.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From TSE IP usage and concept point of view, Arria 10 and Cyclone 10 are the same.

To run the example design in Cyclone 10, one can port over the Arria 10 example design to target Cyclone 10 device. i.e. by changing the device OPN, transceiver RX/Tx pin assignments, clock pin assignment, regenerate the IP and design in Quartus.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

From now we have taking the same approach as you suggested. Their is a doubt regarding one IP . That IP name is Avalon Memory Mapped Master translator IP. It is not included in IP catalog of Quartus 2 prime pro. You have any document or design example from where i can use it.

Thanks for reply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can refer to below Platform Designer user guide, see section '5.1.3.2. Avalon Memory Mapped Host Translator'

https://www.intel.com/content/www/us/en/docs/programmable/683609/21-3/creating-a-system-with.html

Depends on the Quartus version you are using, the previous component could be has been renamed.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page