- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Looking how to infer a small ROM into MLAB. When using the following code, the resulting altsyncram still reports RAM_BLOCK_TYPE set to AUTO instead of MLAB. I use the following code, tries romstyle on q and rom with same results, AUTO resulting into M10K being used. All assignments are default.

// ROM Test

// Quartus Prime Verilog Template

// Single Port ROM

// Declare the ROM variable

(* romstyle="mlab"*) reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0]; /* */

reg [(ADDR_WIDTH-1):0] addr_reg;

initial

begin

$readmemb("baseline.txt", rom);

end

// Initialize the ROM with $readmemb. Put the memory contents

// in the file single_port_rom_init.txt. Without this file,

// this design will not compile.

// See Verilog LRM 1364-2001 Section 17.2.8 for details on the

// format of this file, or see the "Using $readmemb and $readmemh"

// template later in this section.

always @ (posedge clk_50)

begin

addr_reg <= addr;

q <= rom[addr_reg];

end

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I would like to duplicate the issue. May I know what edition (Pro/Standard) and version you are using?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello KhaiY,

I'm using Quartus Standard 18.0 for Windows. Here is my full code snipet if you wish to reproduce. Three scenarios:

- Code as is, all settings default, it results in the ROM being implemented with one M10K.

- romstyle removed, all settings default, it results in the ROM being implemented generic logic due to its small size. (Uninfered RAM logic)

- romstyle removed, "allow rom size recognition: on", it results int the ROM being implemented with one M10K

Example Code:

module ROM_init

#(parameter DATA_WIDTH=8, ADDR_WIDTH=5)

(

input clk_50,

input [(ADDR_WIDTH-1):0] addr,

output [(DATA_WIDTH-1):0] q_o,

output [(DATA_WIDTH-1):0] p

);

// ROM Test

// Quartus Prime Verilog Template

// Single Port ROM

assign q_o = q;

// Declare the ROM variable

reg [(DATA_WIDTH-1):0] q;

(* romstyle="mlab"*) reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

reg [(ADDR_WIDTH-1):0] addr_reg;

initial

begin

$readmemb("baseline.txt", rom);

end

always @ (posedge clk_50)

begin

addr_reg <= addr;

q <= rom[addr_reg];

end

// IP Catalog version for comparisson

//rom1port rom1port_inst (

//.address ( addr ),

//.clock ( clk_50 ),

//.q ( p )

//);

endmodule

// For reference baseline.txt is as follow:

/*

00000000

00000001

00000010

00000011

00000100

00000101

00000110

00000000

00000000

00001000

00010000

00100000

01000000

10000001

10000010

00000000

00000001

00000010

00000011

00000100

00000101

00000110

00001000

00010000

00100000

01000000

10000001

00001000

00010000

00001000

*/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know what device you are using? It would be great if you could provide the QAR archive file as it contains all the settings same as your design file. To generate the archive file, click on Project > Archive Project

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

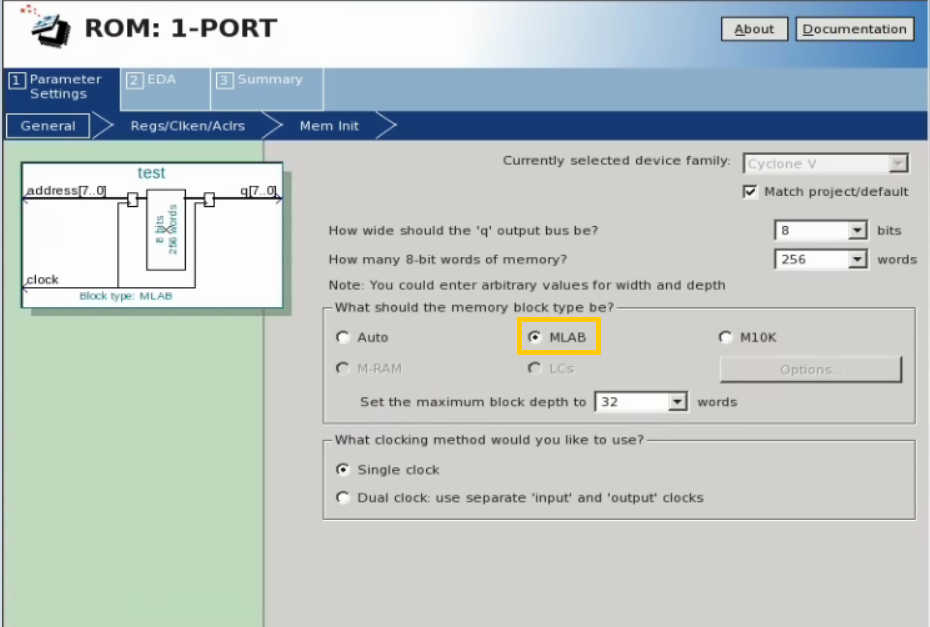

I can duplicate the error, the ROM type is set to AUTO even the romstyle="MLAB" attribute is used. I tried to set the romstyle to "M10K", the ROM type is set to M10K in the Fitter report under RAM Summary, which is the correct behavior. I think this is the error on MLAB setting only. I will file a case to engineering for this error. Thanks for reporting this to us. Coud you use the IP Catalog to instantiate ROM with MLAB type as a temporary workaround?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you are able to proceed with the temporary workaround?

Thanks.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page