Calculating Channel Loss from DDRx Batch Wizard Results

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Community

- Intel Community Knowledge Base

- Product Support Forums Knowledge Base

- FPGA Knowledge Base

- FPGA Wiki

- Calculating Channel Loss from DDRx Batch Wizard Results

Calculating Channel Loss from DDRx Batch Wizard Results

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Calculating Channel Loss from DDRx Batch Wizard Results

About the Channel Loss Calculation Tool

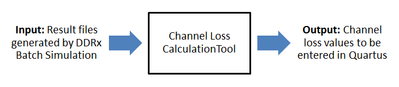

The Channel Loss Calculation Tool helps to analyze the results generated by the HyperLynx DDRx Batch Simulation Wizard when used to simulate external memory interfaces. The input to the tool is the result of Excel files generated by the HyperLynx DDRx Batch Simulation. The output of the tool is the calculated channel loss values needed in the Arria 10 External Memory Interface IP.

Channel Loss Calculation Tool flow.

c/cd/Channel_Loss_Calculation_Tool_flow.png

Channel Loss Calculation Example

To use this tool, perform the following steps:

1. Download the Channel Loss Calculation Tool, located below, and place it in the desired directory.

2. Download the DDRx Batch Simulation results, located below, and place it in the desired directory.

3. Open the Channel Loss Calculation Tool and enable macros if prompted.

4. Click on the Import Data button and navigate to the directory where the DDRx Batch Simulation results are stored. Open the DDR_Results<timestamp> folder and click OK. For this example, open the DDR_Results_Jun-9-2015-11h-03m folder and click OK.

5. Click on the Run Program button and enter the memory clock frequency when prompted. For this example, enter 1066MHz and click OK.

NOTE: If an error message appears stating the HyperLynx files could not be found, but the tool is still able to import the data and run - the error message can be ignored.

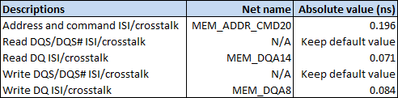

You should now see the calculated channel loss numbers to be entered in Quartus during the IP generation process.

Calculated channel loss values.

Entering Results in Quartus

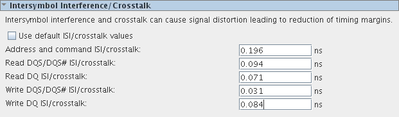

To enter these calculated parameters in Quartus for an Arria 10 EMIF IP, click on the Board Timing tab and enter the values into the Intersymbol Interface/Crosstalk section.

Board Timing ISI/Crosstalk parameters for Arria 10 EMIF IP.

Resource Files

- Channel Loss Calculation Tool: Download Channel Loss Tool

Locate under Board Design and System-Level Timing Closure > Board Simulation > Channel Loss Tool

- Example: DDRx Batch Simulation results - See Attached

Link to setup Quartus generated IBIS files for use with HyperLynx

Community support is provided Monday to Friday. Other contact methods are available here.

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice.