Calculating Channel Loss from DDRx Batch Wizard Results

Sucesso! Subscrição adicionada.

Sucesso! Subscrição removida.

Desculpe, você precisa verificar para concluir esta ação. Clique no link de verificação no seu e-mail. Você pode reenviar por meio de seu perfil.

- Intel Community

- Intel Community Base de conhecimento

- Product Support Forums Base de conhecimento

- FPGA Base de conhecimento

- FPGA Wiki

- Calculating Channel Loss from DDRx Batch Wizard Results

Calculating Channel Loss from DDRx Batch Wizard Results

- Subscrever fonte RSS

- Marcar como novo

- Marcar como lido

- Marcador

- Subscrever

- Página amigável para impressora

- Denunciar conteúdo inapropriado

Calculating Channel Loss from DDRx Batch Wizard Results

About the Channel Loss Calculation Tool

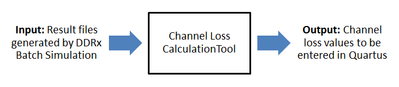

The Channel Loss Calculation Tool helps to analyze the results generated by the HyperLynx DDRx Batch Simulation Wizard when used to simulate external memory interfaces. The input to the tool is the result of Excel files generated by the HyperLynx DDRx Batch Simulation. The output of the tool is the calculated channel loss values needed in the Arria 10 External Memory Interface IP.

Channel Loss Calculation Tool flow.

c/cd/Channel_Loss_Calculation_Tool_flow.png

Channel Loss Calculation Example

To use this tool, perform the following steps:

1. Download the Channel Loss Calculation Tool, located below, and place it in the desired directory.

2. Download the DDRx Batch Simulation results, located below, and place it in the desired directory.

3. Open the Channel Loss Calculation Tool and enable macros if prompted.

4. Click on the Import Data button and navigate to the directory where the DDRx Batch Simulation results are stored. Open the DDR_Results<timestamp> folder and click OK. For this example, open the DDR_Results_Jun-9-2015-11h-03m folder and click OK.

5. Click on the Run Program button and enter the memory clock frequency when prompted. For this example, enter 1066MHz and click OK.

NOTE: If an error message appears stating the HyperLynx files could not be found, but the tool is still able to import the data and run - the error message can be ignored.

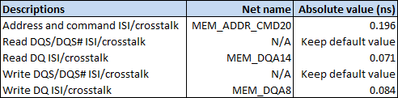

You should now see the calculated channel loss numbers to be entered in Quartus during the IP generation process.

Calculated channel loss values.

Entering Results in Quartus

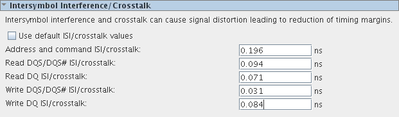

To enter these calculated parameters in Quartus for an Arria 10 EMIF IP, click on the Board Timing tab and enter the values into the Intersymbol Interface/Crosstalk section.

Board Timing ISI/Crosstalk parameters for Arria 10 EMIF IP.

Resource Files

- Channel Loss Calculation Tool: Download Channel Loss Tool

Locate under Board Design and System-Level Timing Closure > Board Simulation > Channel Loss Tool

- Example: DDRx Batch Simulation results - See Attached

Link to setup Quartus generated IBIS files for use with HyperLynx

O suporte à comunidade é fornecido de segunda a sexta-feira. Outros métodos de contato estão disponíveis aqui.

A Intel não verifica todas as soluções, incluindo (mas não se limitando a) quaisquer transferências de arquivos que possam aparecer nesta comunidade. Assim, a Intel se isenta de todas as garantias explícitas e implícitas, incluindo, sem limitação, as garantias implícitas de comercialização, adequação a um propósito específico e não violação, bem como qualquer garantia decorrente de curso de desempenho, curso de negociação ou uso no comércio.

Para obter informações mais completas sobre otimizações do compilador, consulte nosso Aviso de otimização.