Disabling DCFIFO Embedded Timing Constraints for older device families

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Community

- Intel Community Knowledge Base

- Product Support Forums Knowledge Base

- FPGA Knowledge Base

- FPGA Wiki

- Disabling DCFIFO Embedded Timing Constraints for older device families

Disabling DCFIFO Embedded Timing Constraints for older device families

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

- Title: Disabling DCFIFO Embedded Timing Constraints for older device families

- Description: This forum article is dedicated to help users that are suspect of DCFIFO functional issues in older Intel PSG (Altera) FPGA families like Stratix III, Stratix II, Stratix, Cyclone IV, Cyclone III, Cyclone II, and Cyclone FPGAs.

- This article is in reference to the following KDB:

Why do I see incorrect functionality in hardware for my DCFIFO and Mixed-Width DCFIFO Megafunction?

- The following qsf will not be valid when compiling a project device family that is not listed in the above KDB.

set_global_assignment -name DISABLE_EMBEDDED_TIMING_CONSTRAINT ON

- For Quartus version 15.1 and later

- Look for the COMPONENT dcfifo in top level RTL generated by Quartus IP megawizard.

i.e. If you created the DCFIFO using the Megawizard and named it DCFIFO_TEST1, it will generate a high level DCFIFO_TEST1.vhd file.

- Inside the top level file, add the following lpm_hint, in bold, to the COMPONENT dcfifo if it is not already there:

COMPONENT dcfifo

GENERIC (

intended_device_family : STRING;

lpm_hint : STRING;

lpm_numwords : NATURAL;

lpm_showahead : STRING;

- In the instantiation for the component inside the top level file, add the following in bold:

dcfifo_component : dcfifo

GENERIC MAP (

intended_device_family => "Cyclone IV E",

lpm_hint => "DISABLE_DCFIFO_EMBEDDED_TIMING_CONSTRAINT=TRUE",

lpm_numwords => 256,

lpm_showahead => "OFF",

- In some instantiations where the lpm_hint already exists, add the disable embedded timing constraint as follows:

dcfifo_component : dcfifo

GENERIC MAP (

intended_device_family => "Cyclone IV E",

lpm_hint => "RAM_BLOCK_TYPE=M9K, DISABLE_DCFIFO_EMBEDDED_TIMING_CONSTRAINT=TRUE",

lpm_numwords => 256,

lpm_showahead => "OFF",

- Compile the design and verify that the following is not found in Timequest, Report SDC. (the red asterics below represent name implementations that could be different depending on the DCFIFO implementation)

set_false_path -from [get_keepers {*rdptr_g*}] -to [get_keepers {*ws_dgrp|dffpipe*|dffe*}]

set_false_path -from [get_keepers {*delayed_wrptr_g*}] -to [get_keepers {*rs_dgwp|dffpipe*|dffe*}]

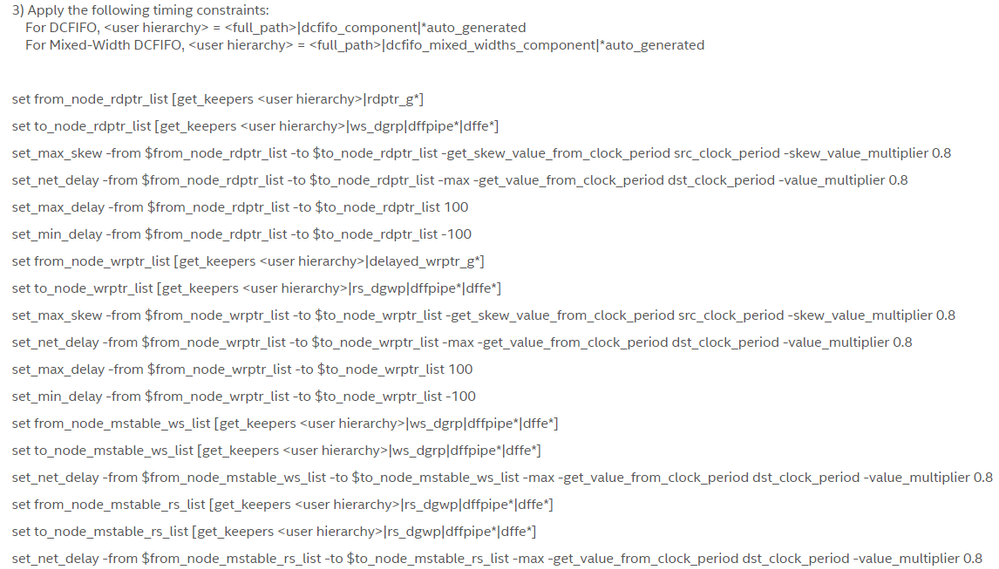

- Next, follow the same instructions in the KDB article "Step 3)" to manually add SDC timing constraints:

Why do I see incorrect functionality in hardware for my DCFIFO and Mixed-Width DCFIFO Megafunction?

- For Quartus versions BEFORE 15.1

- Open Quartus

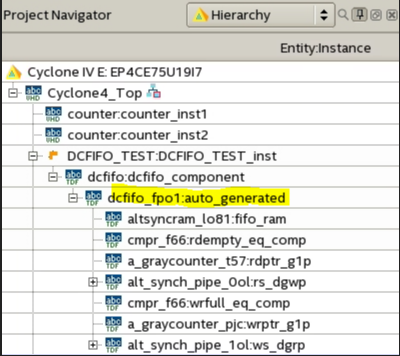

- After synthesizing the design, look for the “dcfifo_component” in the project navigator, and then the next level dcfifo_*:auto_generated tdf file.

- Refer to the picture, dcfifo_hierarchy.PNG

- Double click and open the dcfifo_*:auto_generated file, it should open the file dcfifo_*.tdf.

- In the dcfifo_*.tdf file, search for set_false_path.

- Copy the entire line, paste it just below, and make the modifications similar to the following two lines. The first line is commented out and shows in red the portion that should be removed in the 2nd line.

--OPTIONS ALTERA_INTERNAL_OPTION = "AUTO_SHIFT_REGISTER_RECOGNITION=OFF;REMOVE_DUPLICATE_REGISTERS=OFF;SYNCHRONIZER_IDENTIFICATION=OFF;SYNCHRONIZATION_REGISTER_CHAIN_LENGTH = 2;suppress_da_rule_internal=d101;suppress_da_rule_internal=d102;suppress_da_rule_internal=d103;{-to wrptr_g} suppress_da_rule_internal=S102;{-to wrptr_g} POWER_UP_LEVEL=LOW;-name CUT ON -from rdptr_g -to ws_dgrp|dffpipe_id9:dffpipe15|dffe16a;-name SDC_STATEMENT ""set_false_path -from *rdptr_g* -to *ws_dgrp|dffpipe_id9:dffpipe15|dffe16a* "";-name CUT ON -from delayed_wrptr_g -to rs_dgwp|dffpipe_hd9:dffpipe12|dffe13a;-name SDC_STATEMENT ""set_false_path -from *delayed_wrptr_g* -to *rs_dgwp|dffpipe_hd9:dffpipe12|dffe13a* """;

OPTIONS ALTERA_INTERNAL_OPTION = "AUTO_SHIFT_REGISTER_RECOGNITION=OFF;REMOVE_DUPLICATE_REGISTERS=OFF;SYNCHRONIZER_IDENTIFICATION=OFF;SYNCHRONIZATION_REGISTER_CHAIN_LENGTH = 2;suppress_da_rule_internal=d101;suppress_da_rule_internal=d102;suppress_da_rule_internal=d103;{-to wrptr_g} suppress_da_rule_internal=S102;{-to wrptr_g} POWER_UP_LEVEL=LOW";

- Compile the design and verify that the following is NOT found in Timequest, report SDC. (the red asterics below represent name implementations that could be different depending on the DCFIFO implementation)

set_false_path -from [get_keepers {*rdptr_g*}] -to [get_keepers {*ws_dgrp|dffpipe*|dffe*}]

set_false_path -from [get_keepers {*delayed_wrptr_g*}] -to [get_keepers {*rs_dgwp|dffpipe*|dffe*}]

Community support is provided Monday to Friday. Other contact methods are available here.

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice.