Generating an Intel Agilex® FPGA per pin RLC IBIS (.ibs) file

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Community

- Intel Community Knowledge Base

- Product Support Forums Knowledge Base

- FPGA Knowledge Base

- FPGA Wiki

- Generating an Intel Agilex® FPGA per pin RLC IBIS (.ibs) file

Generating an Intel Agilex® FPGA per pin RLC IBIS (.ibs) file

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Generating an Intel Agilex® FPGA per pin RLC IBIS (.ibs) file

Description

This article is dedicated to Intel® Quartus® Prime Pro Edition Software users who cannot generate Intel Agilex® FPGA ibs files from the EDA Netlist Writer.

Error (20562): Device family does not support board-level IBIS output file generation.

Error: Quartus Prime EDA Netlist Writer was unsuccessful. 1 error, 0 warnings

Previous Intel FPGA families like Intel® Stratix® 10 and Arria® 10 allowed users to run the EDA Netlist Writer to create a project ibs file that contained per pin RLC values, IBIS model lists for each IO Standard, and electrical details for each IO model supported. In Intel Agilex® FPGA, users can use lumped RLC package values, but this is not ideal when modeling higher speed IO interfaces like for DDR4 in board simulation tools like HyperLynx.

This article will show users how to run a post-fitter processing script in the NIOSII command shell to obtain a more detailed per-pin RLC Agilex IBIS file.

Update as of 2/14/2022:

Please check out this 3rd party IBIS generator tool created by CadEnhance.

And a tutorial on how to use the FPGA PIN PLANNER tool to create GPIO IBIS models for Agilex.

CADEnhance How to Build IBIS Models for Intel® AgileX® FPGA Designs

The CADEnhance tools also handle the correct creation of differential pairs.

Differential pairs can also be manually created. The following Knowledge Based Article (KDB) explains how to manually create the [diff pin] section.

Creating the [diff pin] section

Update as of 6/9/2022:

The Gen_agilex_pin_ibis.tcl file has been updated to create a [Pin Mapping] section to enable power-aware IBIS simulations. The latest version of the Gen_agilex_pin_ibis.tcl is 1.2.Intel Agilex® FPGA IBIS information links

To get the files required to generate a pin-specific Agilex ibs file, go here:

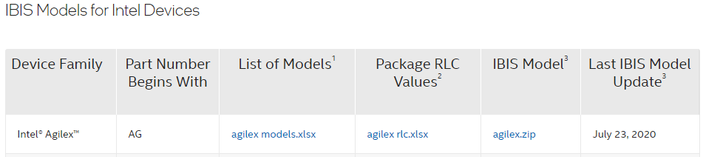

IBIS Models for Intel® FPGA Devices

agilex models.xlsx will download the Excel file agilex-model-list.xlsx.

agilex rlc.xlsx will download the Excel file agilex-pkg-rlc.xlsx

agilex.zip will download the file agilex.zip, which after unzipped, will contain the files agilex.ibs and the IBIS Models User Guide_v1.2.pdf.

The agilex-model-list.xlsx contains the list of all Agilex IO Standards and associated models.

The agilex-pkg-rlc.xlsx contains the lumped package RLC values for each Agilex part number and package combination.

The agilex.ibs file contains the detailed model information for each IO Standard model.

A CUSTOMER MUST WRITE AN IPS CASE OR REQUEST VIA THE FORUMS THE AGILEX PACKAGE-SPECIFIC RLC SPREADSHEET.

For instance, if you are using the following Agilex device:

AGFB027R24C2E2V

You will need to write an IPS case or request via our forums the per-pin package RLC data. The file will be delivered as AGFB027R24C_RLC.xlsx.

All xlsx files should be opened in Excel and then saved out as CSV UTF-8 comma delimited.

Tcl script

The Tcl script Gen_agilex_pin_ibis.tcl can be run to create a project-specific IBIS file for use in board simulation tools like HyperLynx. The script can be found at the bottom of this article. Change .txt to .tcl.

Script Description

The Gen_agilex_pin_ibis.tcl will open 5 different files to create the project-specific ibs file.

1. agilex_GPIO.ibs

2. agilex-pkg-rlc.cvs

3. agilex-model-list.csv

4. AGFB027R24C_RLC.csv (Where AGFB027R24C will be specific to your part/package combination)

5. <project>.pin (Where <project> is the name of your Quartus project)

It first creates the ibs file header, then cross-references the project.pin file with the per pin RLC values found in the pin-specific RLC file that was requested via IPS case or forums. After that, it adds the pin mapping section, which indicates the power and ground bus connections for every pin listed under the pin section. Next, it creates a model selector list allowing users to select the appropriate models for the IO Standard and IO being used. Finally, it adds each model's IBIS specific information to the end of the ibs file.

Running the script

Open a Quartus Prime Pro NIOSII command shell. Navigate to the location of your <project>.pin file. Besides the .pin file, add the first 4 files listed in the previous section to the same directory along with the Gen_agilex_pin_ibis.tcl file.

To run the script from a NIOSII command shell.

quartus_sh.exe -t Gen_agilex_pin_ibis.tcl <project name> <Agilex_RLC csv filename.csv>

Example:

quartus_sh -t Gen_agilex_pin_ibis.tcl ddr4 AGFB027R24C_RLC.csv

Disclaimer

The script has been tested against AGFB027R24C_RLC and AGFB027R25A_RLC projects. Every project is different, and thus it is advised that you check your ibs file results for errors and to run an IBIS file checker like HyperLynx's Visual IBIS Editor.

Community support is provided Monday to Friday. Other contact methods are available here.

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice.