Stratix V Hard IP For PCI Express Instantiation Walkthrough

Готово! Подписка добавлена.

Готово! Подписка удалена.

Извините, вы должны пройти верификацию для завершения этого действия. Нажмите ссылку верификации в своем электронном сообщении. Вы можете повторить отправку через свой профиль.

- Intel Community

- База знаний Intel Community

- База знаний Product Support Forums

- База знаний FPGA

- FPGA Wiki

- Stratix V Hard IP For PCI Express Instantiation Walkthrough

Stratix V Hard IP For PCI Express Instantiation Walkthrough

- Подписка на RSS-канал

- Отметить как новое

- Отметить как прочитанное

- Закладка

- Подписаться

- Страница в формате печати

- Сообщить о недопустимом содержимом

Stratix V Hard IP For PCI Express Instantiation Walkthrough

Overview

This article serves to guide the user through the process of using Quartus II (Qsys), and Modelsim to generate, compile, and simulate the Altera provided PCIe Hard IP design files.

Required Materials

- Quartus II

- ModelSim

- A working knowledge of the use of these programs.

- Stratix V Hard IP for PCI Express User Guide

Walkthrough

- Create a folder to serve as your project directory. This project uses C:\Sandbox\

- Open Quartus II. Then click on the Qsys icon at the top menu bar of the Quartus II main screen. See Figure 1-1.

- Figure 1-1: Quartus II Main Screen /a/ac/Qaurtus_main_screen.png

- Once Qsys opens, go to File > Open. See Figure 1-2. Then navigate to <quartus_installation_directory>/ip/altera/altera_pcie/altera_pcie_hip_ast_ed/example_design/sv

- and then select the PCIe configuration you would like to instantiate.

- Figure 1-2: Default Main Screen for Qsys 4/43/Qsys_Open.png

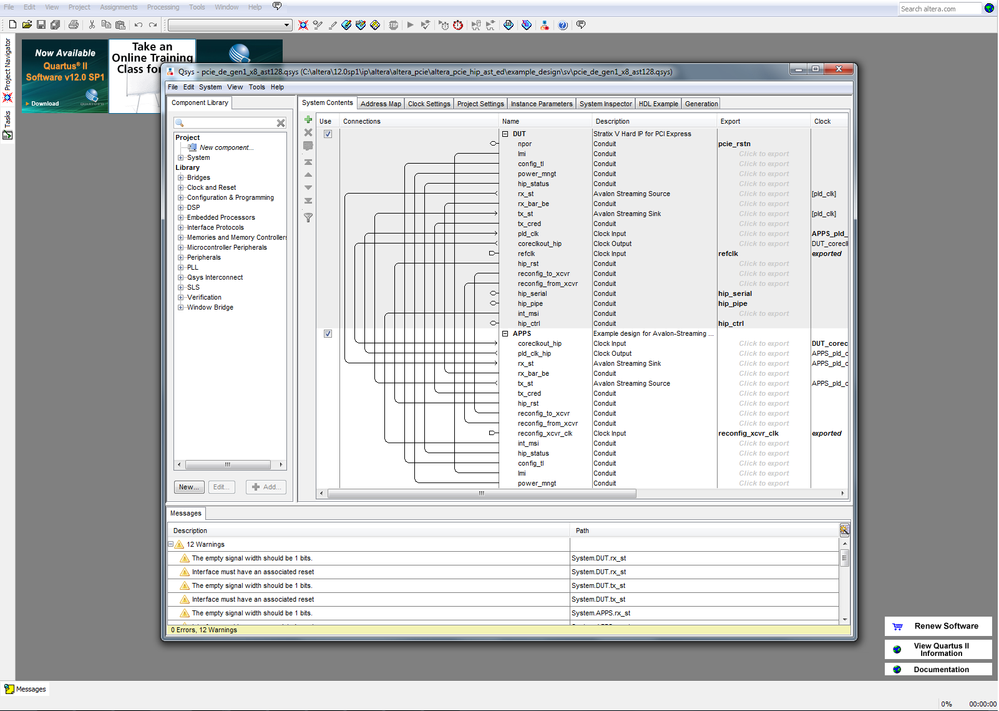

- After you have selected your configuration, a new screenw ill appear similiar to figure 1-3.

- Figure 1-3: Qsys Main Screen After Configuration Is Selected

- Click on the "Generation" tab at the top of the Qsys screen. A screen similiar to Figure 1-4 should appear. For the Simulation settings, choose the HDL language you prefer, and choose Standard BFM's... for the Create Testbench Qsys system option. Choose an output directory (your project directory) and click generate at the bottom of the screen.

- Figure 1-4: Qsys Generation Tab 3/32/Qsys_generation.png

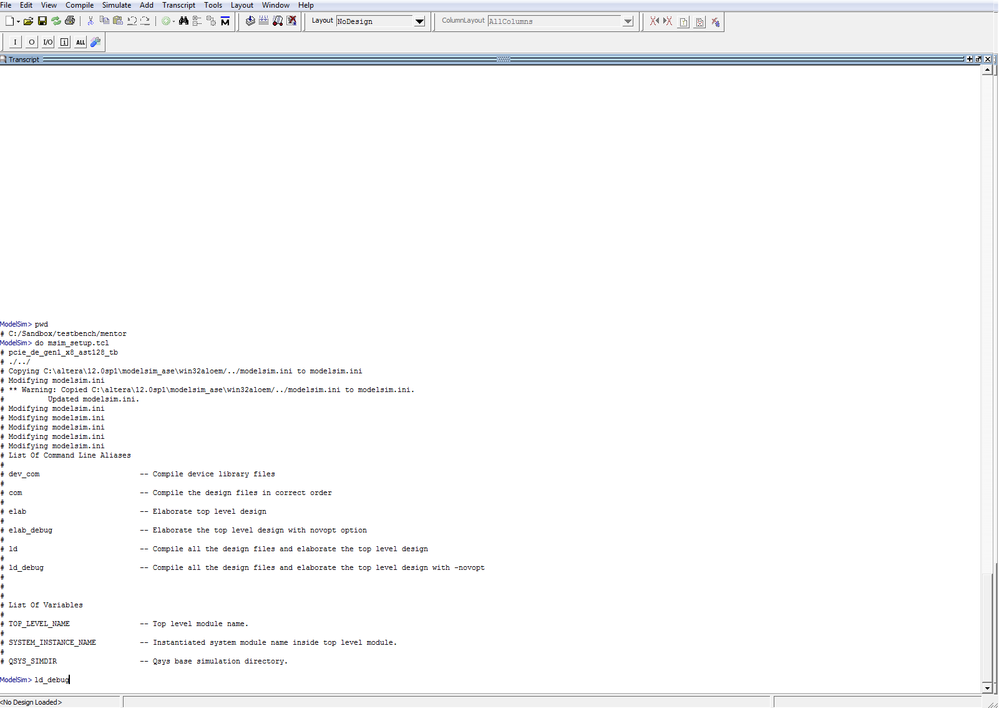

- After the design files have been generated, open ModelSim. Navigate to <project_dir>/testbench/mentor. type "source msim_setup.tcl". This will prepare the .Tcl script that will compile your design. use a combination of the options given to compile the design, or just type "ld_debug" for a full compilation. A screen similiar to Figure 1-5 will appear.

- Figure 1-5: ModelSim Main Screen

- After compilation has completed, add any signals you would like to the wave window, and type "run -all" to run the simulation in its entirety. See Figure 1-6 for an example of how the ModelSim screens should appear after compilation completes.

- Figure 1-6: Main Screen After Compilation Completes 7/71/Modelsim_run_all.png

More Detailed Simulation Readouts

This short article guides the user through instantiating design files that give the user control over how detailed they want the simulation readouts to be, from very detailed, to not so detailed.

Disclaimer

© 2011 Altera Corporation. The material in this wiki page or document is provided AS-IS and is not

supported by Altera Corporation. Use the material in this document at your own risk; it might be, for example, objectionable,

misleading or inaccurate.

Key Words

PCIe, PCI E, PCI Express, Stratix V, SV, S, V, Walkthrough, guide, help, Stratix V GX, Stratix V GT, SV, SVGX, SVGT, S5GX, S5GT, S5, Stratix 5, Stratix 5 GX, StratixV, StratixV GX, Stratix5, Stratix5 GX, Altera, generated, generation, Instantiation, creation, design, files, Hard, IP,

Community support is provided Monday to Friday. Other contact methods are available here.

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Для получения более полной информации об оптимизации компилятора см. Уведомление об оптимизации.