- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

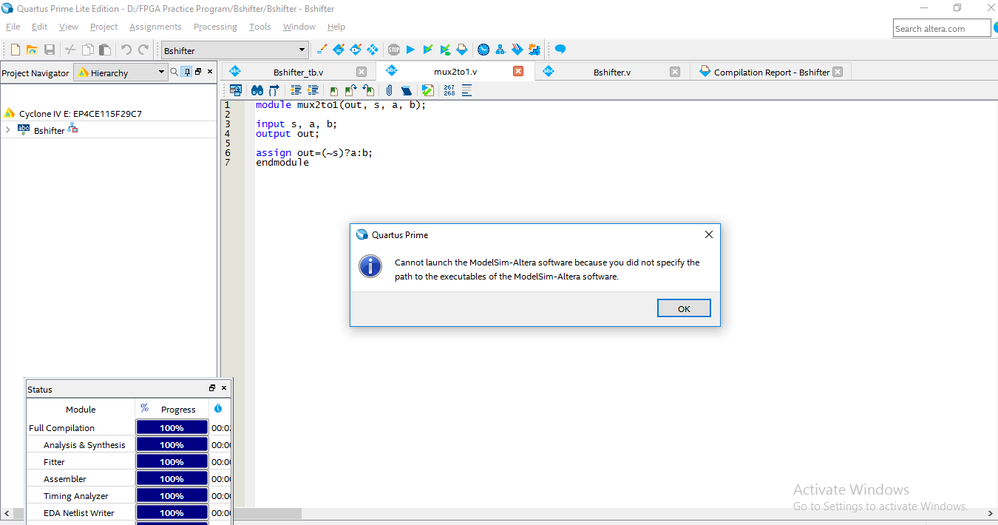

I have compiled a project in Altera and want to simulate the same using ModelSim-Altera software. I have already selected the ModelSim as a default simulator in the project setting so that it can simulate the design after compilation. However, the compilation stops at 83% as it is not able to simulate the project. I tried to simulate it manually but this message appears:

Would anyone suggest how to resolve this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

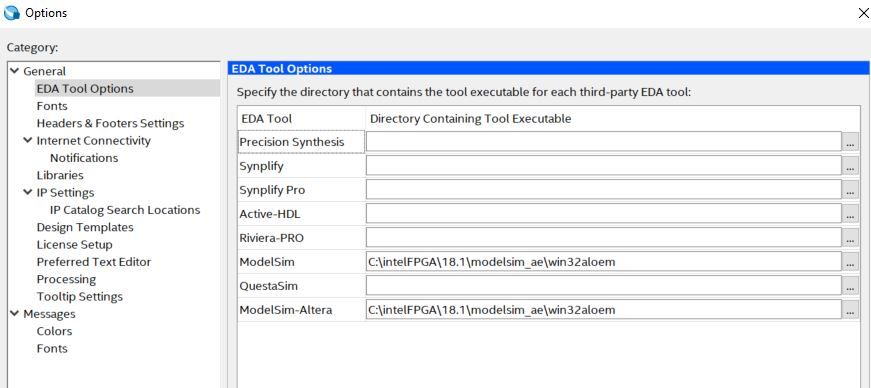

Go to Tools > Options > EDA Tool Options.

Check that the path to the ModelSim-Altera software is correctly set to: <install_directory>\win32aloem (for example, C:\intelFPGA\18.1\modelsim_ae\win32aloem)

p.s. Don’t forget to Reply, and Select the Best Solution. :)

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Go to Tools > Options > EDA Tool Options.

Check that the path to the ModelSim-Altera software is correctly set to: <install_directory>\win32aloem (for example, C:\intelFPGA\18.1\modelsim_ae\win32aloem)

p.s. Don’t forget to Reply, and Select the Best Solution. :)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you so much for the solution, now the modelsim is accessible automatically. However, I am not able to view the waveform. Do I need to add the variables to view waveform. Also, would you please tell me the difference between RTL simulation and Gate Level Simulation? I am sorry if my questions are very basic, I am a beginner therefore having many doubts.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

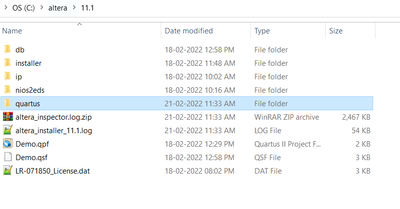

How about Quartus 11.1 version, I can't find any modelsim_ase folder in the installed directory.

Please check the below image.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good morning,

On my PC, I am using the version of 13.1 Quartus II software and I followed the above step as per this version . But still it's not working.

and when we click the RTL simulation it shows "Native link error".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You might need to provide further detail on why you are not able to view the waveform. Try to go through an example design/online tutorial to check where goes wrong.

RTL simulation is to check the design functionality without taking into account the delays of the lookup tables. Gate level simulation can also be zero delays but is more often used in unit delay or full timing mode.

Post-synthesis and post-fit gate-level simulations run significantly slower than RTL simulation. Intel FPGA recommends that you verify your design using RTL simulation for functionality and use the Timing analyzer for timing.

You can learn more about simulation from the link below:

https://www.intel.com/content/www/us/en/programmable/documentation/gft1513990268888.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply. It helped a lot.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page