- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have a design where we control an external RAM memory. We generate the CLK and control memory signals in a FPGA (Cyclone IV). The CLK signal is generated using a PLL, with 180º phase shift.

The design is working but we have detected that "set_output_delay" dosen't apply. For example, we have compared, in an oscilloscope, the delay beetwen the signals CLK and a bit ADD[15] bus and it is constant for any "set_out_delay".

We are using the next constrains configuration:

create_clock -name RAM_CLK -period 16 [get_ports {RAM_CLK}]

create_generated_clock -name vt_RAM_CLK -source [get_ports {RAM_CLK}] -divide_by 1 -multiply_by 1 -phase 180

set_output_delay -clock {vt_RAM_CLK} 3 [get_ports {RAM_ADD[15] }].

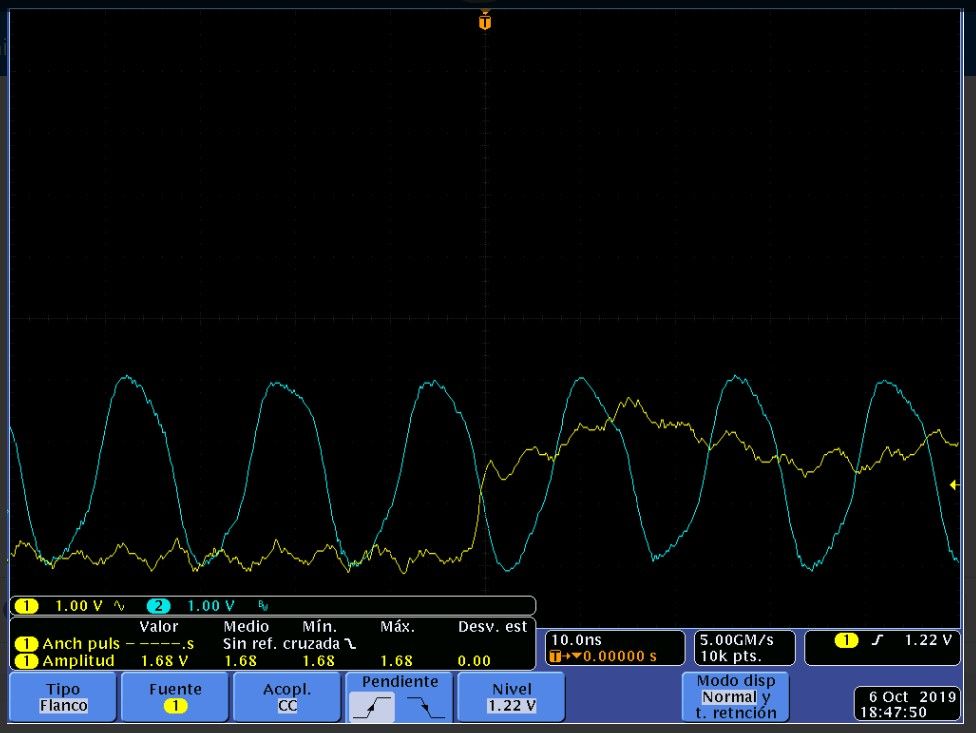

In next figure, you can see timing of both signals.

The delay is contant for any "output_delay" value (0, 1, 2, 3..).

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The delay is the same becuase the register is located in the I/O. The dalay from the register to the port is the same. Do you see timing violation when you set the output delay value to 12 and higher? If you move this register out of the I/O, you will see some differences in your oscilloscope.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks. I was confused with some terms.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You are welcome.

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »