- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am following the tutorial that presents an introduction to PLATFORM DESIGNER tool (link bellow)

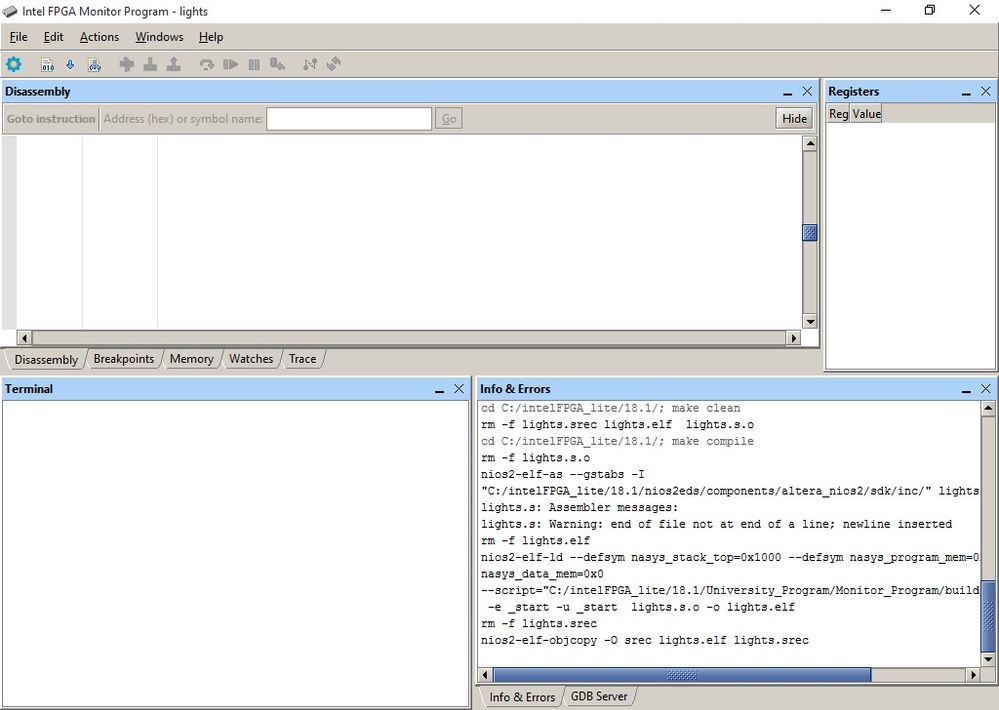

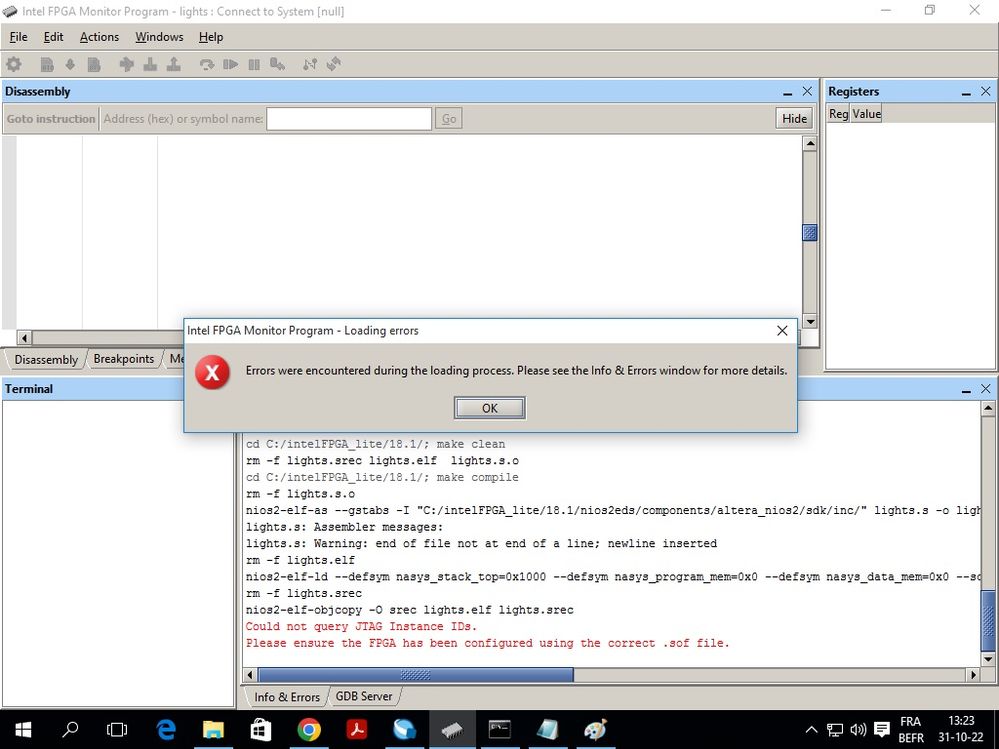

Everything is OK till the last step (in step 9 page 31), when selecting "Actions > Compile & Load" , an error message appears says:

"could not query jtag instance ids, please ensure the fpga has been configured using the correct .sof file."

I am using:

*Quartus prime Lite edition 18.1.

* Intel FPGA Monitor Program 18.1.

*DE2-115 board.

on Win 10.

Please any one have fixed this problem.

Regards...

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Check this link https://habr.com/ru/post/464795/

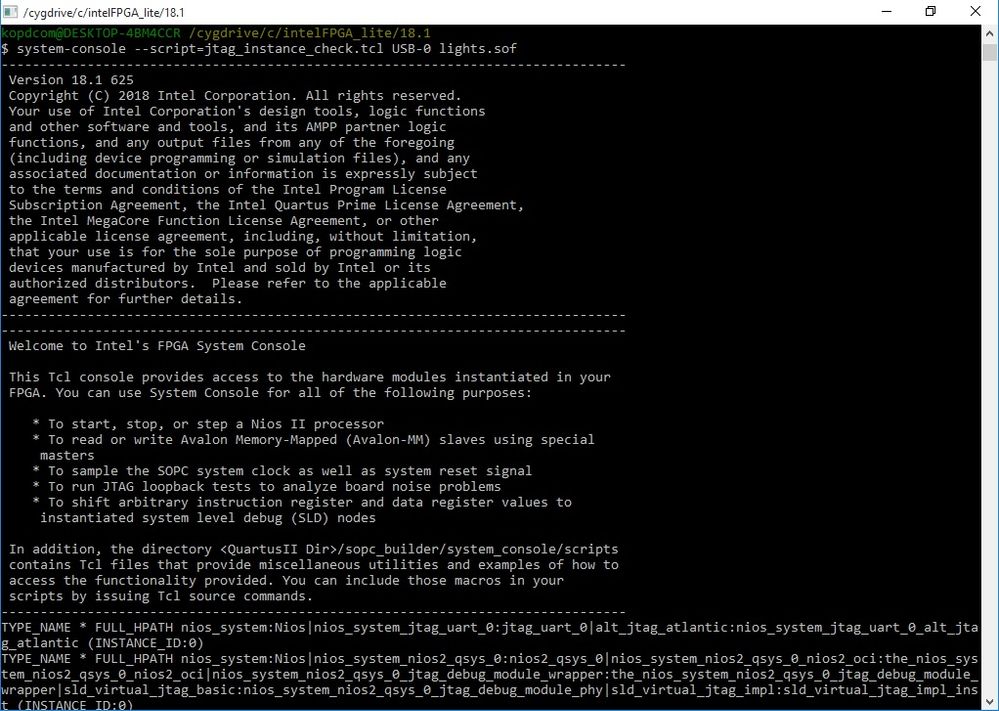

Tried to open the NIOS II console:

There I went to the directory where the sof file is located and entered the command line:

system-console --script=jtag_instance_check.tcl USB-0 <file_name>.sof

For the command line above, you have to copy the ..\University_Program\Monitor_Program\bin\jtag_instance_check.tcl to the same place where sof is, so as not to suffer with the path. As a result, I got a pretty decent response.

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kopdcom ,

Any further concern or update?

Does the problem being resolved?

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sheng,

Thank you a lot for taking my request into consideration.

Sorry for being late to response, but actually, I have to wait till sunday to access to our Lab and try the solution.

Thank you again, and a feedback will be sent in sunday.

with best regards...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have followed step by step as you mentionned ( https://habr.com/ru/post/464795/ ). a same message appears in the nios II console when following the steps of the solution and typing the instruction:

system-console --script=jtag_instance_check.tcl USB-0 <file_name>.sof

The message looks like:

TYPE_NAME * FULL_HPATH nios_systeme:Nios|nios_system_jtag_quart_0....................(INSTANCE_ID:0)

TYPE_NAME * FULL_HPATH nios_systeme:Nios|nios_system_nios2_qsys_0...................(INSTANCE_ID:0)

Unfortunatly, the error message still occur:

"could not query jtag instance ids, please ensure the fpga has been configured using the correct .sof file."

But, it should to mentionned that before doing this solution, I could not selecting COMPILE or LOAD separatly in the monitor program (in ACTIONS tab) juste I could select COMPLE & LOAD, but now, I can chose COMPILE, and it's OK, but when choosing LOAD after COMPILE, the previous error return.

I hope that I have well clarified.

Regards...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kopdcom ,

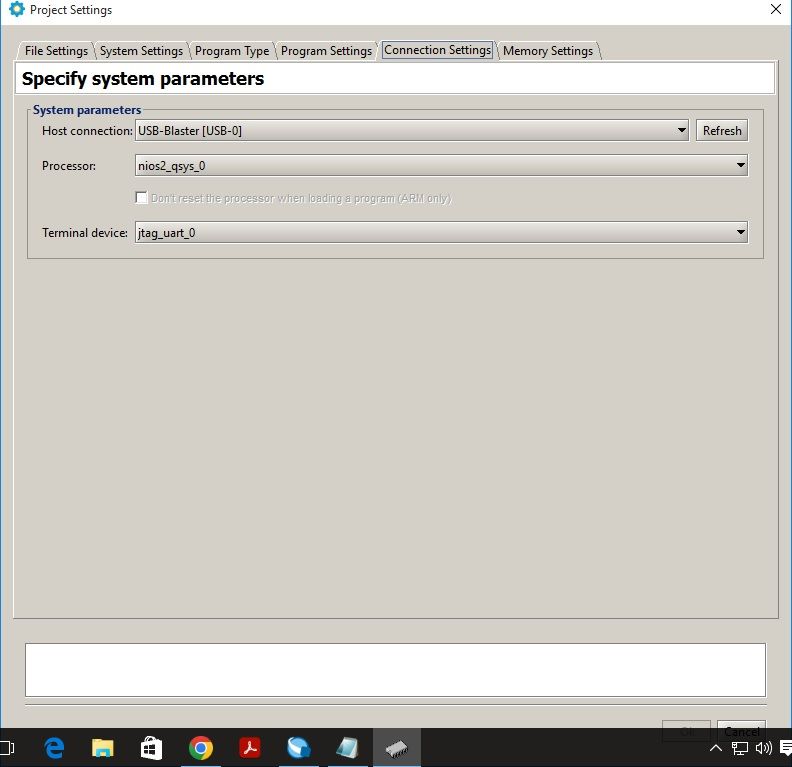

Are you using USB-1 for Host connection image below?

May be have to use this system-console --script=jtag_instance_check.tcl USB-1 <file_name>.sof

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sheng,

I have confirmed, It's USB-0.

I will try the next solution...

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kopdcom ,

Or try to replace the code section below in tcl script jtag_instance_check.tcl:

# PRINT OUT INSTANCE ID INFO FOR EVERYTHING:

set i 0

foreach path [lsort -command compare_node_number [get_service_paths bytestream]] {

# If this path corresponds to a JTAG UART, incr i

if {[string match *$cable_name* $path ] && [string match *jtag_uart* [marker_get_type $path] ]} {

puts "[marker_get_info $path] (INSTANCE_ID:$i)"

incr i

}

}

set i 0

foreach path [lsort -command compare_node_number [get_service_paths processor]] {

# If this path corresponds to a NiosII, incr i

if {[string match *$cable_name* $path ] && [string match *nios2* [marker_get_type $path] ]} {

puts "[marker_get_info $path] (INSTANCE_ID:$i)"

incr i

}

}

With the code section below:

# PRINT OUT INSTANCE ID INFO FOR EVERYTHING:

set i 0

foreach path [lsort -command compare_node_number [get_service_paths bytestream]] {

# If this path corresponds to a JTAG UART, incr i

if {[string match *$cable_name* $path ] && [string match *jtag_uart* [marker_get_type $path] ]} {

set info [marker_get_info $path]

if {[string first "|" $info] == -1} {

set info [string map {"FULL_HPATH " "FULL_HPATH a:b|"} $info]

}

puts "$info (INSTANCE_ID:$i)"

incr i

}

}

set i 0

foreach path [lsort -command compare_node_number [get_service_paths processor]] {

# If this path corresponds to a NiosII, incr i

if {[string match *$cable_name* $path ] && [string match *nios2* [marker_get_type $path] ]} {

set info [marker_get_info $path]

if {[string first "|" $info] == -1} {

set info [string map {"FULL_HPATH " "FULL_HPATH a:b|"} $info]

}

puts "$info (INSTANCE_ID:$i)"

incr i

}

}

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sheng,

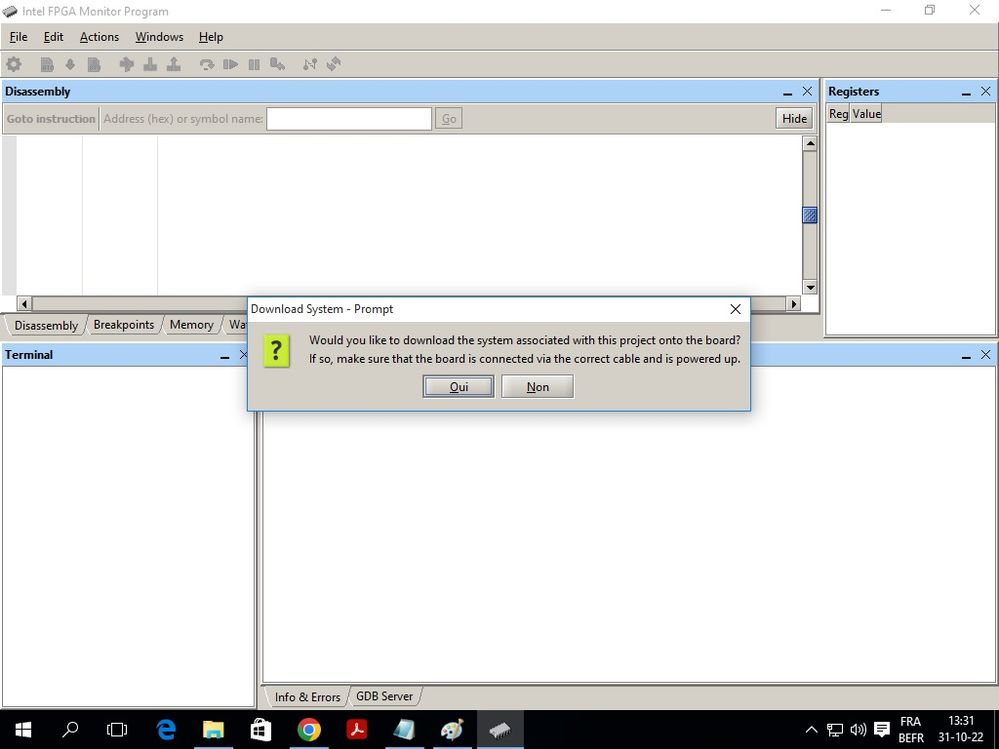

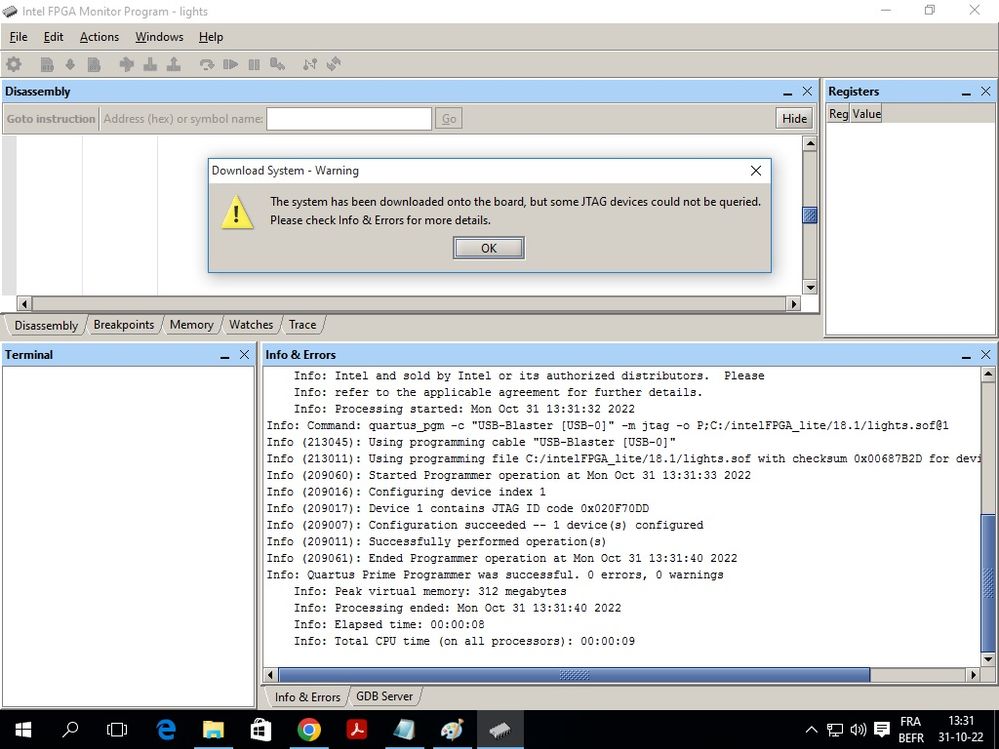

I have replaced the code section mentionned in jtag_instance_check.tcl, unfortunatly, still the same error message. I have made screen-prints of all steps:

** Nios II Console:

** Downloading the system associated with the project:

-----------------------------------------------------Info& Erros:-----------------------------------------------------

C:/intelFPGA_lite/18.1/quartus/bin64/quartus_pgm -c "USB-Blaster [USB-0]" --auto

1) USB-Blaster [USB-0]

020F70DD 10CL120(Y|Z)/EP3C120/..

Info: *******************************************************************

Info: Running Quartus Prime Programmer

Info: Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Info: Copyright (C) 2018 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the applicable agreement for further details.

Info: Processing started: Mon Oct 31 13:49:56 2022

Info: Command: quartus_pgm -c "USB-Blaster [USB-0]" -m jtag -o P;C:/intelFPGA_lite/18.1/lights.sof@1

Info (213045): Using programming cable "USB-Blaster [USB-0]"

Info (213011): Using programming file C:/intelFPGA_lite/18.1/lights.sof with checksum 0x00687B2D for device EP4CE115F29@1

Info (209060): Started Programmer operation at Mon Oct 31 13:49:57 2022

Info (209016): Configuring device index 1

Info (209017): Device 1 contains JTAG ID code 0x020F70DD

Info (209007): Configuration succeeded -- 1 device(s) configured

Info (209011): Successfully performed operation(s)

Info (209061): Ended Programmer operation at Mon Oct 31 13:50:04 2022

Info: Quartus Prime Programmer was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 312 megabytes

Info: Processing ended: Mon Oct 31 13:50:04 2022

Info: Elapsed time: 00:00:08

Info: Total CPU time (on all processors): 00:00:10

------------------------------------------------------------------------------------------------------------------------

** After choosing COMPILE (in ACTIONS tab):

** After choosing LOAD (in ACTIONS tab):

Regards...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kopdcom ,

Sorry for misdirection. For Monitor Program, supposedly have to follow this document link below (located in ..\University_Program\Monitor_Program\tutorial\Intel_FPGA_Monitor_Program_NiosII.pdf

and have to use DE1-SoC device.

Steps summary:

- Creating a Project

- Specify a system: DE1-SoC Computer. It is represented by .sopcinfo and .sof files which are automatically included when this computer is selected. The DE1-SoC preloader is also automatically selected.

- Specify a program type: Assembly Program. Click on the selection Include a sample program with the project. Select the program named Simple Program.

- Specify program details: the source code file(s) associated with this program is listed in the Source files box.

- Specify system parameters: DE-SoC [USB-1]

- Specify program memory settings

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sheng,

It is written in the first page of this tutorials:

"In this tutorial it is assumed that the reader has access to the Intel DE1-SoC Development and Education board, connected to a computer that has Quartus Prime and Nios II Embedded Design Suite (EDS) software

installed".

But in our Lab, we have just the DE2-115 board. So I want to know if this tutorial is just for the DE1-SoC Board or I can try it on DE2-115.

Regards...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes. The configuration in that particular tutorial is just mainly for DE1-SoC Board. There are also other systems available for Monitor Program which are DE0-CV, DE0-Nano, DE0-Nano-SoC, DE10-Lite and DE10-Nano.

Best regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Or may be you can try the Computer Systems with Nios II Teaching Material check the link https://www.intel.com/content/www/us/en/developer/topic-technology/fpga-academic/materials-computer-systems.html. This will have DE2-115 board available.

Document link: https://ftp.intel.com/Public/Pub/fpgaup/pub/Intel_Material/18.1/Computer_Systems/DE2-115/DE2-115_Computer_NiosII.pdf

Thanks,

Best regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will try it.

Thank you very much.

Regards...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page