- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

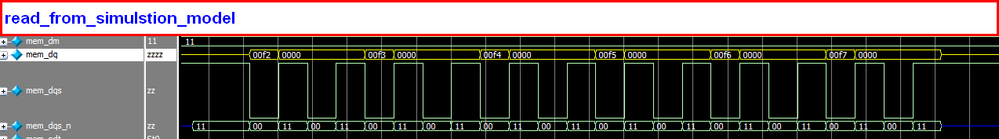

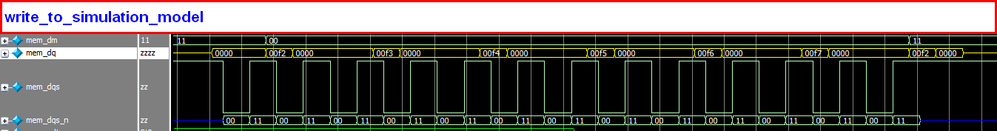

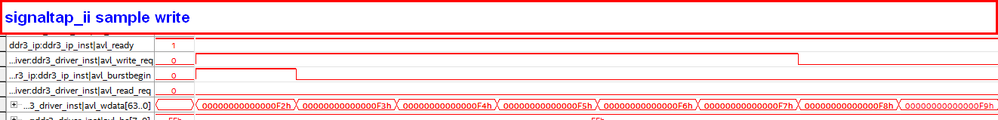

The FPGA I use belongs to Stratix iv, ddr3 belongs to Mircon, ddr3 's clock is 300mhz, the width of DQ is 16 bits.Both write bursts and read burst addresses are maintained at 0, and burst lengths are 6.I wrote the same data continuously in ddr3, wrote a burst of action, and began to read. When I simulate and use the simulation model given by the example, the data I write is the same as the data I read, and when I use the actual FPGA, the data written and read is somewhat different, but not completely wrong.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There are couple of reasons that I can think why it may failed on hardware but passed on sim.

- Can you check your Quartus design to ensure it's timing clean with positive margin on Quartus timequest DDR report ?

- Pls ensure all DDR3 IP setting is set correctly (DDR3 timing parameter, board setting) that matched with your board layout and DDR3 DRAM used.

- Another factor will be to review your board schematic design. Either wrong DDR3 connection on board or certain FPGA power or DDR3 SDRAM is not power up correctly.

- Lastly could be also due to bad signal integrity on board. You need to probe DQ, DQS, address or command bus to double check

Alternately, you can also try using DDR3 example design (that matched with your DDR3 SDRAM setting) generated from UNIPHY IP to test on your board to see if it make a difference.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page