- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm learning how to optimize C++ code for efficient high-level synthesis.

I'm looking at the memory banking code provided in Quartus Prime Pro hls/examples/tutorials folder.

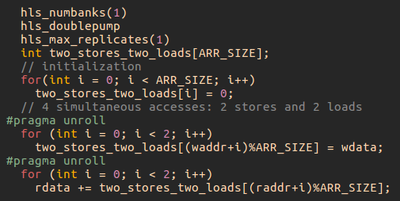

One piece of code is shown like below:

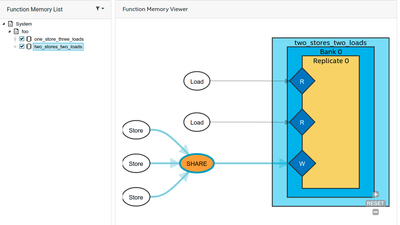

According to what I understand, this should generate single memory bank with two store ports and two load ports. However, when opening the synthesis report, memory view shows as below:

First I can understand the initialization store can reuse the same store ports with the other two stores.

What I don't understand is why the other two stores share the same store port.

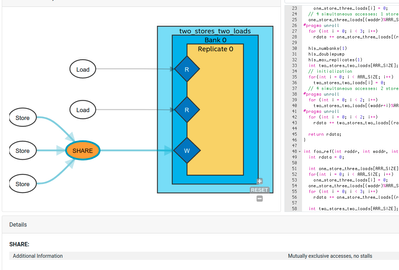

And when I click the share symbol, it says at the bottom, accesses are mutually exclusive, no arbitration? How can the two stores be mutually exclusive?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @BigHandsomeBee,

Thank you for posting in Intel community forum and hope this message find you well.

The behavior you are noticing should be part of the HLS merging memories trying to reduce area required.

Please do refer to the following details explanation here and hope it helps you to understand better.

Best Wishes

BB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @BigHandsomeBee,

Greetings, unfortunately as we do not receive any further clarification on what is provided. Hence thread will now be transitioned to community support. If you have new queries, please feel free to open a new thread and we will be right with you. Otherwise, the community users will further help you with doubts in this thread. Pleasure having you here.

Best Wishes

BB

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page