- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

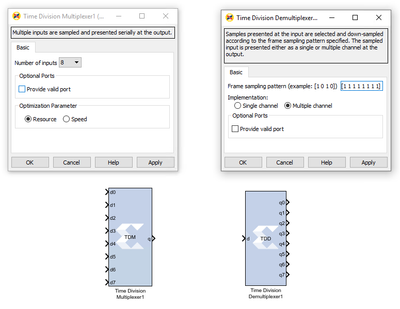

I am porting a project over from Xilinx System Generator to DSPBuilder advanced blockset. Xilinx system generator includes three handy blocks that do not seem to be present in DSP Builder Advanced blockset, both shown below in order: The Downsample block and the TDM/TDD (Time-Division-Mux/Demux) blocks.

What is the simplest and best way to use the available primitive blocks in the DSP Builder Advanced Blockset to build each of these blocks? I imagine one may leverage some kind of FIFO/Sample-and-Hold block for the downsample block, and some kind of counter connected to a mux/demux for the TDM and TDD blocks.

Best,

- Gheorghe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may need a dual clock FIFO to transfer data between two different clock domains.

Regards -SK

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The design flow for DSP Builder may be slightly different from others. The downsampling block is not available from the DSP builder library, however, for simulation purposes, you can use the downsample block from DSP System Toolbox. You can see the example design “demo_firs” example at this directory “installation path\quartus\dspba\Examples\Filters” is using it for simulation purposes (not part of the RTL).

For the TDM, probably you can refer to the DEMUX/MUX block from the primitive library.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you SengKok

About the downsampling block: Does this imply that Intel DSP Builder subsystems cannot be "multirate"? I would like to integrate the downsampling block in my DSPBuilder-generated RTL. Maybe can you refer me to a triggered sample-and-hold block in the DSPBA Blockset to accomplish this?

Thank you,

- Gheorghe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, about the TDM block:

Perhaps I can use the ChanView block in the DSPBA blockset? Do you see any problems with using this block? I suspect that this block won't work because it is reserved for RTL simulations in MATLAB, and does not actually get implemented in DSPBuilder-generated RTL.

Best,

- Gheorghe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The DSP builder system is support single clock domain, and there is NO down or up sampling block as I can see. For the TDM block, you may consider to use the DEMUX in primitive library, it has the same function as ChanView.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you sure that Intel DSP Builder subsystems only support single clock domain?

This video seems to suggest otherwise.

https://youtu.be/stKdxz802GA?t=1249

At the 20:50 mark, the video references another training video called "Building MultiRate DSP Builder Design Training", but I cannot seem to find this other "Multirate" video/training document anywhere?

If you know more about this, please let me know, thank you.

- Gheorghe S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Multirate means the sample rate variation at different stages of a datapath, but it uses a single path clock domain.

The ModelIP block like CIC, decimation FIR or Interpolating FIR are running at different data rates between the input and output port, however, the clock domain is still the same.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, I see, thank you for the clarification.

Is there a way to change a signal's data rate without using these multirate filters?

How can I use the DSPBA blockset to downsample a signal's data rate by only sparsely sampling it at the lower data rate? I would like to avoid perturbing my signals' frequency content by avoiding these filters.

Best,

-Gheorghe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You probably need to use the ModelPrim library to build it, there is a list of components that you can use to customize based on your design requirement (e.,g create a counter to control the valid signal to drop off those unnecessary samples).

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the suggestion.

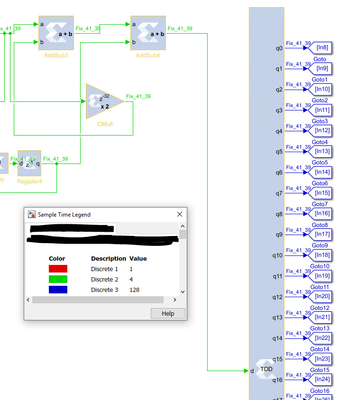

I decided to downsample my data signal by simply feeding it to a separate DSPBuilder-generated IP core running at a lower clock rate. Using the 0L latch block in DSPBA blockset to sample-and-hold my signals does not achieve the downsampling functionality that I am looking for, as this sample-and-hold algorithm adds high frequency content to my signal with jagged stair steps, as opposed to simply undersampling my signal.

Do you have any tips on how to implement a super-sampling mux and an undersampling demux?

Examples of these systems implemented with the Xilinx System Generator Blockset (similar to DSPBA blockset but for Xilinx FPGAs) is shown below.

The mux shown below has 32 input signals, which are outputted as a supersampled signal running at 32x the clock frequency of the input signals.

The demux shown below has one input signal which is time-division-demuxed to output to 32 signals, each at 32x lower clock frequency.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm not familiar with third party tool, however, It looks similar to the DEMUX and MUX block in the primitive library, But please remind that the DSP Builder Advance block set uses only a single clock domain.

For example:

MUX: If the input sample rate is 1/3 of the system clock rate, and there are three input ports. On every clock cycle, you can use the "S" signal to select which input data to go out first and then followed by second and third. This means the input data is without TDM, but the output data can with TDM.

DEMUX: Reverse of MUX. The input data is with TDM, however, the output sample is without TDM.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear SengKok,

Thank you for the clarification.

In attempting to use DSP Builder to build a multirate system, I attempted to generate two DSP Builder custom components, each operating on a different clock domain, and connect data signals between the two custom components in platform designer.

Unfortunately it seems like it is not possible to connect conduit interfaces which are on different clock domains? Please see the attached screenshot below, which contains an error message highlighted.

Is there a workaround for this? Maybe create another clock port on my "NCO..." custom component, and associate this slower clock with the output signals I intend to send to the slower clock "mixer_128..." custom component?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may need a dual clock FIFO to transfer data between two different clock domains.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok thank you.

Using a secondary clock, and associating it to output signals going to a custom component with lower clock rate seems to work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will set this forum case to close-pending for now. The status will remain in this state for 15 calendar days, simply post a note in this forum and it will be reopened for further investigation.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page