- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

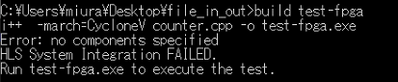

I want to use intelhlscompiler for high-level synthesis of C++ files, but I get the following error.

intelhlscompiler

Quatusprimelite17.1

visualstudio2010

The procedure is

start_intelhls.bat

→ build.bat

→test-x86-64.exe

→build test-fpga

→Error as shown in the image above.

The cpp file I want to use for high level synthesis

↓

------------------------------------------------------------------------------------------------------------

#include "HLS/hls.h"

#include <stdio.h>

int main(void)

{

FILE * fp=NULL;

int seisuu=0; // 数字1

int seisuu2=0; // 数字2

int ans=0;

fp = fopen("input.txt", "r");

if(fp == NULL) {

printf("ファイルを開くことが出来ませんでした.¥n");

}

while (fscanf(fp, "%d,%d", &seisuu,&seisuu2) != EOF)

{

printf("%d %d\n", seisuu,seisuu2);

}

ans = seisuu+seisuu2;

fp = fopen("output.txt", "w");

fprintf(fp,"%d",ans);

fclose(fp);

return 0;

}

-------------------------------------------------------------------------------------------------------------

buid.bat

↓

-------------------------------------------------------------------------------------------------------------

@Echo off

set "SOURCE_FILES=fileinout.cpp"

set "HLS_CXX_FLAGS="

:: This batch file will compile the example design to three standard targets:

:: 1) test-msvc Compile the example design to the CPU

:: Uses Visual Studio 2010

:: 2) test-x86-64 Compile the example design to the CPU

:: Uses the Intel HLS Compiler

:: 3) test-fpga Synthesize the example design to HDL

:: Generates a cosimulation executable to simulate the HDL

:: Uses the Intel HLS Compiler

:: 4) clean Remove any temporary files generated by the compiler

:: Usage: build.bat <target>

:: Example: build.bat test-x86-64

:: Only one argument expected

if not "%2"=="" goto usage

:: Accept the user's target, else default to x86-64

if not "%1"=="" (

set "TARGET=%1"

) else (

set "TARGET=test-x86-64"

echo No target specified, defaulting to %TARGET%

echo Available targets: test-x86-64, test-fpga, test-msvc, clean

)

:: Any tools installed with HLS can be found relative to the location of i++

for %%I in (i++.exe) do (

set "HLS_INSTALL_DIR=%%~dp$PATH:I"

)

set "HLS_INSTALL_DIR=%HLS_INSTALL_DIR%.."

:: Set up the compile variables

if "%TARGET%" == "test-x86-64" (

set "CXX=i++"

set "CXXFLAGS=%HLS_CXX_FLAGS% -march=x86-64"

set "LFLAGS=-o %TARGET%.exe"

) else if "%TARGET%" == "test-fpga" (

set "CXX=i++"

set "CXXFLAGS=%HLS_CXX_FLAGS% -march=CycloneV -ghdl

set "LFLAGS=-o %TARGET%.exe"

) else if "%TARGET%" == "test-msvc" (

set "CXX=cl"

set "CXXFLAGS=/I ""%HLS_INSTALL_DIR%\include"" /nologo /EHsc /wd4068 /DWIN32 /MD"

set "LFLAGS=/link ""/libpath:%HLS_INSTALL_DIR%\host\windows64\lib"" hls_emul.lib /out:%TARGET%.exe"

) else if "%TARGET%" == "clean" (

del /S /F /Q test-msvc.exe test-fpga.exe test-fpga.prj test-x86-64.exe > NUL

rmdir /S /Q test-fpga.prj > NUL

goto:eof

) else (

goto usage

)

:: Replace "" with " in the flags

set "CXXFLAGS=%CXXFLAGS:""="%"

set "LFLAGS=%LFLAGS:""="%"

:: Kick off the compile

echo %CXX% %CXXFLAGS% %SOURCE_FILES% %LFLAGS%

%CXX% %CXXFLAGS% %SOURCE_FILES% %LFLAGS%

if not ERRORLEVEL 0 (

echo Error: Compile failed

exit /b 1

)

echo Run %TARGET%.exe to execute the test.

:: We're done!

goto:eof

:: Dump the usage if we get unexpected input

:usage

echo Usage: build.bat [target]

echo Targets: test-msvc, test-x86-64, test-fpga, clean

echo Example: build.bat test-x86-64

exit /b 2

-------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, you need to identify the function in your application, you may also read Table 3:

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You need to mark the part of your code that as going to run on the FPGA as a "component". You should carefully study the following document, specially sections 2 and 3:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/hls/ug-hls.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, you need to identify the function in your application, you may also read Table 3:

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page