- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi everyone,

the FPGA report fails for a simple kernel for the matrix transpose operation. The output asks me to

PLEASE submit a bug report to https://software.intel.com/en-us/support/priority-support and include the crash backtrace.

But the web page does not work well for me. Thus, I attach the error messages and source code here.

- The source code: attached.

- The optimization report:

icpx -fsycl -fintelfpga -DFPGA_HARDWARE -std=c++2b -Wall -Wextra -Wpedantic -Werror -O3 mattrans.cpp -Xshardware -fsycl-link=early -Xsv -Xsparallel=16 -Xsffp-reassociate -Xsffp-contract=fast -o mattrans.a

- The error messages:

Dependency files for SYCL source and SYCL-source library: /dev/shm/icpx-32a212/mattrans-1ee627.d

aoc: Environment checks completed successfully.

aoc: Selected target board package /opt/software/FPGA/IntelFPGA/opencl_sdk/20.4.0/hld/board/bittware_pcie/s10_hpc_default

aoc: Selected target board p520_hpc_sg280l

aoc: Processing SPIR-V....

aoc: SPIR-V processing completed

aoc: Linking Object files....

Device information not found: 1SG280LU3F50E1VGS1

aoc: Optimizing and doing static analysis of code...

PLEASE submit a bug report to https://software.intel.com/en-us/support/priority-support and include the crash backtrace.

Stack dump:

0. Program arguments: /opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt -march=fpga -O3 -ipatemplate /opt/software/FPGA/IntelFPGA/opencl_sdk/20.4.0/hld/board/bittware_pcie/s10_hpc_default/hardware/p520_hpc_sg280l/board_spec.xml -board /opt/software/FPGA/IntelFPGA/opencl_sdk/20.4.0/hld/board/bittware_pcie/s10_hpc_default/hardware/p520_hpc_sg280l/board_spec.xml -vpfp-relaxed -sycl -dbg-info-enabled --soft-elementary-math=false -pass-remarks-output=pass-remarks.yaml mattrans.1.bc -o mattrans.kwgid.bc

1. Running pass 'Function Pass Manager' on module 'mattrans.1.bc'.

2. Running pass 'Mark the decision for loop pipelining' on function '@ZTS15mattrans_kernel'

Stack dump without symbol names (ensure you have llvm-symbolizer in your PATH or set the environment var `LLVM_SYMBOLIZER_PATH` to point to it):

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(+0x29c600f)[0x55f1186f700f]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(+0x29c2f1d)[0x55f1186f3f1d]

/lib64/libpthread.so.0(+0x12ce0)[0x1517e8435ce0]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl6MemDep25BasicMemoryDependenceInfo24distinctTermsInLoopNestsEPN4llvm4LoopERNS_16VariableGEPIndexES4_S6_+0x436)[0x55f1193b00f6]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl6MemDep25BasicMemoryDependenceInfo38distinctTermsInDifferentLoopIterationsEPN4llvm11InstructionElRKSt6vectorINS_16VariableGEPIndexESaIS6_EEmS4_lSA_mPNS2_4LoopE+0x1952)[0x55f1193b25f2]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl6MemDep25BasicMemoryDependenceInfo38distinctTermsInDifferentLoopIterationsEPN4llvm11InstructionERKNS_24AddressDecompositionInfoES4_S7_+0xb6)[0x55f1193b3486]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl6MemDep25BasicMemoryDependenceInfo21analyzeDecompositionsEPN4llvm11InstructionES4_bb+0xe4c)[0x55f1193b6a8c]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl6MemDep31LoopCarriedMemoryDependenceInfo13getDependenceEPN4llvm11InstructionES4_b+0xc0c)[0x55f1193bc03c]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl6MemDep31LoopCarriedMemoryDependenceInfo13getDependentsEPN4llvm11InstructionERNS2_11SmallPtrSetIS4_Lj2EEEb+0x2de)[0x55f1193be96e]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl33LoopCarriedDepsBeforePipelineInfo12process_loopEPKN4llvm4LoopE+0x54d)[0x55f119527e0d]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl16LoopPipelineInfo19check_serial_regionEPKN4llvm4LoopE+0x64)[0x55f11951da74]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN3acl16LoopPipelineInfo19runPipelineAnalysisEPNS_13ArrayPrivInfoEPNS_33LoopCarriedDepsBeforePipelineInfoEPNS_14LocalMemConfigEPNS_20RestrictInterleavingE+0xc3)[0x55f119521953]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN20MarkPipelineDecision3runEv+0x4c)[0x55f119a7100c]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN30MarkPipelineDecisionLegacyPass13runOnFunctionERN4llvm8FunctionE+0x3cd)[0x55f119a718cd]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN4llvm13FPPassManager13runOnFunctionERNS_8FunctionE+0x3eb)[0x55f117ca1f8b]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN4llvm13FPPassManager11runOnModuleERNS_6ModuleE+0x39)[0x55f117ca2199]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_ZN4llvm6legacy15PassManagerImpl3runERNS_6ModuleE+0x2fb)[0x55f117ca2aeb]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(main+0x20d4)[0x55f116bb3d44]

/lib64/libc.so.6(__libc_start_main+0xf3)[0x1517e4337cf3]

/opt/software/FPGA/IntelFPGA/oneapi/23.1.0/compiler/2023.1.0/linux/lib/oclfpga/llvm/aocl-bin/aocl-opt(_start+0x29)[0x55f116cde119]

Error: Optimizer FAILED.

Refer to /dev/shm/mattrans-96129e-fe9b4d/mattrans.log for details.Many thanks

Xin

Ссылка скопирована

- « Предыдущий

-

- 1

- 2

- Следующий »

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

i will check and update to you

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

sorry for delaying. because of the workload, I was not able to respond to your issue.

if you don't mind may I know which document are you following? please share the document link.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

@hareesh wrote:if you don't mind may I know which document are you following? please share the document link.

I did not mention any documents in my questions.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

with shared information, i am not able to identify the issue. so, I am asking which document are you following.

i need some more information like what are trying to do and tool details, following steps.

please share the requested information.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

> i am not able to identify the issue

The issue is clearly shown in "the error messages" in my question (see above).

> so, I am asking which document are you following.

I did not mention any document in my question.

> i need some more information like what are trying to do and tool details, following steps.

My question indicates it clearly that the FPGA kernel does matrix transpose operation and the tool is icpx. The source code and steps to compile it are also clearly given in my question.

Please read my question carefully before asking questions!

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

I didn't receive any response from you. could please share the requested information it may help us to identify the issue.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

I am trying to duplicate your issue so I need some more time.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

> I am trying to duplicate your issue so I need some more time.

1. download the DPC++ source code attached in the question.

2. execute the "icpx ..." line in the question.

To re-produce the issue takes 1 min in my opinion.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

same issue I also facing in my local machine. I need to discourse with the team.

and one more question shared code, is your own code or already available code in intel?

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

> is your own code or already available code in intel?

Its my own code.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

OK. just discussing with team and need some more time

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

I am waiting for a response from the team.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

follow the above page. On this page, you can see step-by-step instructions to execute.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi, your link is irrelevant to my question.

- my question is about matrix transpose, but your link is about matrix multiply

- my question is about FPGA programming, but your link is about CPU and GPU

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi @xwuupb,

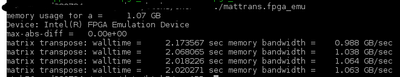

Apologies for the confusion, with the provided source code we have managed to successfully run the emulator compilation. With that we can rule out the issues on the code.

Hence based on the error message provided above it seems to be mentioning about hardware device info not found.

Suspecting that the targeted hardware are not mention appropriately in the compilation command.

For full system compilation which I assume is the case here the BSP are required, for the supported BSP devices you may refer to the link below:

- https://www.intel.com/content/www/us/en/developer/tools/oneapi/fpga.html (For non PAC product, please scroll to the 'Choose an FPGA Platform' section)

- https://www.intel.com/content/www/us/en/docs/oneapi/programming-guide/2023-1/fpga-bsps-and-boards.html (For PAC product)

Hope that clarify, please do let us know if situation are still misunderstood.

Regards

BB

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

thank you for your answer! I think it may be a problem with the BSP shipped with the Bittware 520N card with Intel Stratix 10 GX 2800 FPGA. In the static report stage, if I give the compiler option -Xstarget with

- the BSP for the Bittware 520N card, it fails with the error messages shown in my question (see the first thread of this topic).

- the BSP of intel_s10sx_pac:pac_s10_usm, it succeeds in the report stage.

Does that make sense?

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

any update?

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi @xwuupb,

If I remember correctly the mention 'intel_s10sx_pac:pac_s10_usm' are BSP for Intel PAC D5005, and suspect there would be some interconnect differences. (Note: no hard trying to compile and program but likely it would fail or not behaviour correctly)

Noted on the hardware involved, unfortunately as it is coming from Bittware, we would need them to provide the correct workable BSP to continue. Hence would suggest to get in touch with their support channels and provide them with the references design you are using to understand further.

Hope that clarify.

Best Wishes

BB

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

do you have any queries?

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Страница в формате печати

- « Предыдущий

-

- 1

- 2

- Следующий »