- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi there,

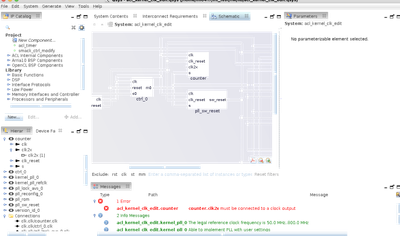

I am currently using Intel HLS Quartus 15.1 offline compiler to compile the customised circuit and I came across an issue.

I do not want to use the clock2x in the BSP components acl_kernel_clk.qsys, and hence I just use my own version of acl_timer.

However when performing logic synthesis of Opencl kernel, the error occurs that my own kernel goes to infinite recursion.

Then I tried to unconnect clock2x in the acl_tiemr module of the acl_kernel_clk but the qsys component just gives error.

May I ask how can I safely remove the clock2x in the acl_kernel_clk.qsys module? I really need to remove it because I need clock outputs of plls to do something else.

If not, does anyone have any suggestion of replacing the acl_timer module with self-defined module?

Thank you in advance!

Mingqiang

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I have solved the problem by connecting clock2x to an unused clock ports, this issue is thus solved.

- 태그:

- SOLVED

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I have solved the problem by connecting clock2x to an unused clock ports, this issue is thus solved.

- 태그:

- SOLVED

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Thanks for closing the loop on your issue and posting the answer here for others to see. It will be beneficial for others who may face the same problem. Thanks again.