- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm trying to to use Avalon ST interface to stream data between an OpenCL kernel and RTL module. The avalon ST interface stream data always when ovalid=1 and oready =1 as mentioned in the first example of OpenCL library (Intel design example).

MY Question is: How can I to stop the streaming ? should I send a zero to ovalid and oready (ovalid=0 and oready =0). ?

If Yes, I wrote the code below but my RTL module still receiving data from kernel and data are processing. I activate ovalid and oready with an enable signal. So ovalid and oready will be high when enable =1 and o if not. here is the code:

ovalid <= enable & 1'b1 ; oready<= enable & 1'b1;

Even with enable=0 my RTL still processing data like ovalid=1 ? if not how I can stop sending data between my RTL module and

the OpenCL Kernel?

Thanks,

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Since your source is the OpenCL kernel and RTL is the sink ,

can you make iready as invalid.So that the data streaming can be stopped.

Please let us know the results after trying this.

Thanks and Stay Safe

Anil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply. But iready and ivalid are inputs in my RTL (not outputs), which means I can just read them, I cannot make ireaday as invalid ?

How to set them ? how to manipulate them ? thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I want to clarify the question:

The question is: Can I drop the transfer of data from my RTL to the OpenCL kernel according to a condition that I can set, while receiving all inputs from the OpenCL kernel.

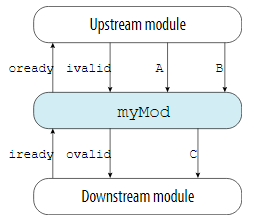

An example based in the first example of the Intel OpenCL advanced library and it presented in the programming guide (please see the figure below) : In this example, Can I drop the transfer of C while receiving all my A and B data. If Yes, with which signal because C is always sent aven if ovalid signal =0 ? Thanks,

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Sorry for the late answer,

It turns out that If you have declared your RTL as stall free component this scenario can occur, can you share the .XML file in which you have defined the properties of the RTL module.

Thanks and Regards

Anil

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page