- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

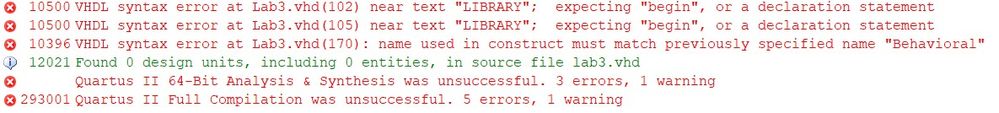

I've been slowly knocking things out of my error list, but I'm stuck on these. Thanks in advance for any assistance.

My code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity freq_div is

Port( clockwide: in STD_LOGIC;

reset : in STD_LOGIC;

clock : out STD_LOGIC);

end freq_div;

architecture Behavioral of freq_div is

signal ctr_int : unsigned(25 downto 0);

signal edge_int: STD_LOGIC;

begin

process(reset, clockwide)

begin

if(reset ='0') then

ctr_int <= "00000000000000000000000000";

edge_int <= '0';

elsif rising_edge(clockwide) then

if(ctr_int= 50000000) then

edge_int <= not edge_int;

ctr_int <= "00000000000000000000000000";

else

ctr_int <= ctr_int+ 1;

end if;

end if;

end process;

clock <= edge_int;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tenbit_ctr is

Port(reset: in STD_LOGIC;

enable : in STD_LOGIC;

clock: in STD_LOGIC;

count_int: out STD_LOGIC_VECTOR (9 downto 0));

end tenbit_ctr;

architecture Behavioral of tenbit_ctr is

signal counter : STD_LOGIC_VECTOR(9 downto 0);

begin

process(clock, reset)

begin

if reset='0' then

counter <= "0000000000";

Elsif(clock = '0' and clock'event) then

If enable = '1' then

counter <= counter + 1;

end if;

end if;

end process;

count_int <= counter;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity Counterde1 is

Port(CLOCK_50 : in STD_LOGIC;

KEY: in STD_LOGIC_VECTOR (3 DOWNTO 0);

SW : IN STD_LOGIC_VECTOR (9 DOWNTO 0);

LEDR : OUT STD_LOGIC_VECTOR (9 DOWNTO 0);

HEX0,HEX1,HEX2,HEX3 : out

STD_LOGIC_VECTOR(0 to 6));

end Counterde1;

architecture Behavioral of Counterde1 is

signal count_int: std_logic_vector(9 downto0);

signal clockwide: STD_LOGIC;

signal clock : STD_LOGIC;

signal reset : STD_LOGIC;

signal enable : STD_LOGIC;

signal HEXOUT : STD_LOGIC_VECTOR (20 downto 0);

COMPONENT freq_div

Port(clockwide: in STD_LOGIC;

reset : in STD_LOGIC;

clock : out STD_LOGIC);

end COMPONENT;

COMPONENT tenbit_ctr

Port (reset : in STD_LOGIC;

clock : in STD_LOGIC;

enable :in STD_LOGIC;

count_int: out STD_LOGIC_VECTOR (9 DOWNTO 0));

end COMPONENT;

COMPONENT disp_ROM

Port( address: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

clock: IN STD_LOGIC := '1';

q: OUT STD_LOGIC_VECTOR(20 DOWNTO 0));

end COMPONENT;

LIBRARY ieee;

USE ieee.std_logic.all;

LIBRARY altera_mf;

use altera_mf;

ENTITY disp_ROM IS

PORT

(

address: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

clock: IN STD_LOGIC := '1';

q: OUT STD_LOGIC_VECTOR (20 DOWNTO 0)

);

END disp_ROM;

ARCHITECTURE SYN OF disp_ROM IS

SIGNAL sub_wire0: STD_LOGIC_VECTOR (20 DOWNTO 0);

COMPONENT altsyncram

GENERIC (

address_aclr_a: STRING;

clock_enable_input_a: STRING;

clock_enable_output_a: STRING;

init_file: STRING;

intended_device_family: STRING;

lpm_hint: STRING;

lpm_type: STRING;

numwords_a: NATURAL;

operation_mode: STRING;

outdata_aclr_a: STRING;

outdata_reg_a: STRING;

widthad_a: NATURAL;

width_a: NATURAL;

width_byteena_a: NATURAL

);

PORT (

address_a: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

clock0: IN STD_LOGIC;

q_a: OUT STD_LOGIC_VECTOR (20 DOWNTO 0)

);

END COMPONENT;

BEGIN

q <= sub_wire0(20 DOWNTO 0);

altsyncram_component: altsyncram

GENERIC MAP (

address_aclr_a=> "NONE",

clock_enable_input_a=> "BYPASS",

clock_enable_output_a=> "BYPASS",

init_file=> "MULDE1.MIF",

intended_device_family=> "Cyclone II",

lpm_hint=> "ENABLE_RUNTIME_MOD=NO",

lpm_type=> "altsyncram",

numwords_a=> 1024,

operation_mode=> "ROM",

outdata_aclr_a=> "NONE",

outdata_reg_a=> "UNREGISTERED",

widthad_a=> 10,

width_a=> 21,

width_byteena_a=> 1

)

PORT MAP (

address_a => address,

clock0 => clock,

q_a => sub_wire0

);

END SYN;

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sami,

- Include begin and end Behavioral; statements in Counterde1 entity(Line 100).

- Line 103, USE ieee.STD_LOGIC_1164.all; not USE ieee.STD_LOGIC.all;

- Line 106, use altera_mf.all; not use altera_mf;

- Line 76 space between downto 0.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity freq_div is

Port( clockwide: in STD_LOGIC;

reset : in STD_LOGIC;

clock : out STD_LOGIC);

end freq_div;

architecture Behavioral of freq_div is

signal ctr_int : unsigned(25 downto 0);

signal edge_int: STD_LOGIC;

begin

process(reset, clockwide)

begin

if(reset ='0') then

ctr_int <= "00000000000000000000000000";

edge_int <= '0';

elsif rising_edge(clockwide) then

if(ctr_int= 50000000) then

edge_int <= not edge_int;

ctr_int <= "00000000000000000000000000";

else

ctr_int <= ctr_int+ 1;

end if;

end if;

end process;

clock <= edge_int;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tenbit_ctr is

Port(reset: in STD_LOGIC;

enable : in STD_LOGIC;

clock: in STD_LOGIC;

count_int: out STD_LOGIC_VECTOR (9 downto 0));

end tenbit_ctr;

architecture Behavioral of tenbit_ctr is

signal counter : STD_LOGIC_VECTOR(9 downto 0);

begin

process(clock, reset)

begin

if reset='0' then

counter <= "0000000000";

Elsif(clock = '0' and clock'event) then

If enable = '1' then

counter <= counter + 1;

end if;

end if;

end process;

count_int <= counter;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity Counterde1 is

Port(CLOCK_50 : in STD_LOGIC;

KEY: in STD_LOGIC_VECTOR (3 DOWNTO 0);

SW : IN STD_LOGIC_VECTOR (9 DOWNTO 0);

LEDR : OUT STD_LOGIC_VECTOR (9 DOWNTO 0);

HEX0,HEX1,HEX2,HEX3 : out

STD_LOGIC_VECTOR(0 to 6));

end Counterde1;

architecture Behavioral of Counterde1 is

signal count_int: std_logic_vector(9 downto 0);

signal clockwide: STD_LOGIC;

signal clock : STD_LOGIC;

signal reset : STD_LOGIC;

signal enable : STD_LOGIC;

signal HEXOUT : STD_LOGIC_VECTOR (20 downto 0);

COMPONENT freq_div

Port(clockwide: in STD_LOGIC;

reset : in STD_LOGIC;

clock : out STD_LOGIC);

end COMPONENT;

COMPONENT tenbit_ctr

Port (reset : in STD_LOGIC;

clock : in STD_LOGIC;

enable :in STD_LOGIC;

count_int: out STD_LOGIC_VECTOR (9 DOWNTO 0));

end COMPONENT;

COMPONENT disp_ROM

Port( address: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

clock: IN STD_LOGIC := '1';

q: OUT STD_LOGIC_VECTOR(20 DOWNTO 0));

end COMPONENT;

begin

end Behavioral;

LIBRARY ieee;

USE ieee.STD_LOGIC_1164.all;

LIBRARY altera_mf;

use altera_mf.all;

ENTITY disp_ROM IS

PORT

(

address: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

clock: IN STD_LOGIC := '1';

q: OUT STD_LOGIC_VECTOR (20 DOWNTO 0)

);

END disp_ROM;

ARCHITECTURE SYN OF disp_ROM IS

SIGNAL sub_wire0: STD_LOGIC_VECTOR (20 DOWNTO 0);

COMPONENT altsyncram

GENERIC (

address_aclr_a: STRING;

clock_enable_input_a: STRING;

clock_enable_output_a: STRING;

init_file: STRING;

intended_device_family: STRING;

lpm_hint: STRING;

lpm_type: STRING;

numwords_a: NATURAL;

operation_mode: STRING;

outdata_aclr_a: STRING;

outdata_reg_a: STRING;

widthad_a: NATURAL;

width_a: NATURAL;

width_byteena_a: NATURAL

);

PORT (

address_a: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

clock0: IN STD_LOGIC;

q_a: OUT STD_LOGIC_VECTOR (20 DOWNTO 0)

);

END COMPONENT;

BEGIN

q <= sub_wire0(20 DOWNTO 0);

altsyncram_component: altsyncram

GENERIC MAP (

address_aclr_a=> "NONE",

clock_enable_input_a=> "BYPASS",

clock_enable_output_a=> "BYPASS",

init_file=> "MULDE1.MIF",

intended_device_family=> "Cyclone II",

lpm_hint=> "ENABLE_RUNTIME_MOD=NO",

lpm_type=> "altsyncram",

numwords_a=> 1024,

operation_mode=> "ROM",

outdata_aclr_a=> "NONE",

outdata_reg_a=> "UNREGISTERED",

widthad_a=> 10,

width_a=> 21,

width_byteena_a=> 1

)

PORT MAP (

address_a => address,

clock0 => clock,

q_a => sub_wire0

);

END SYN;

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page