- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi all,

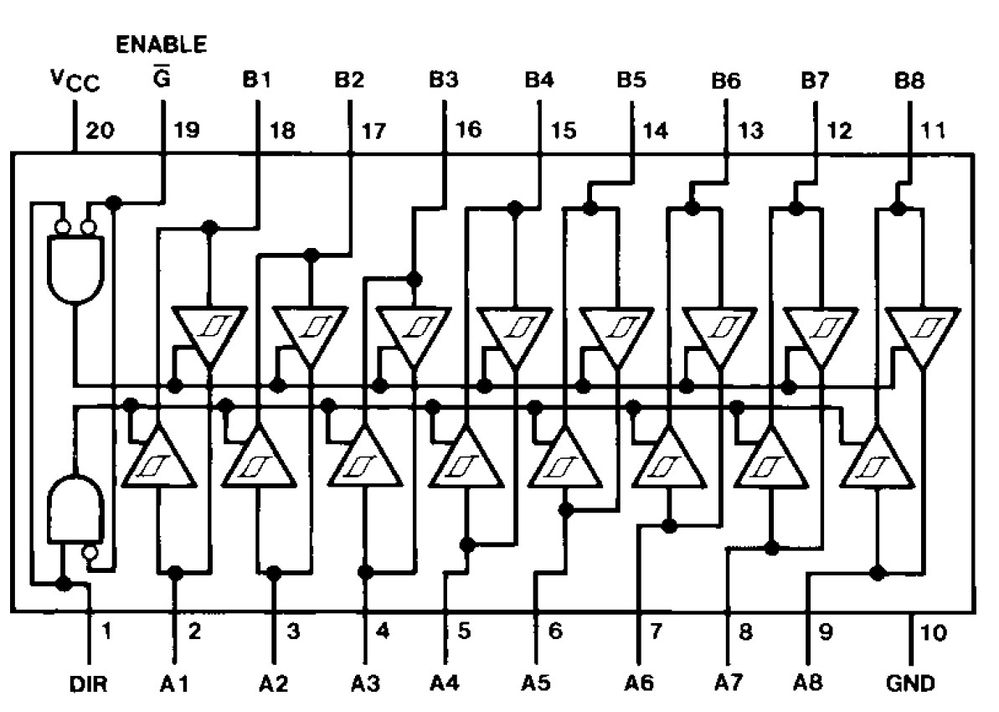

I'm doing some design using schematics block under Quartus 12.1 (as I' not not yet able to wrote HDL) and I was needing to drop on schematics a 74245 octal bus transceiver but I noticed it's missing in the library (also in the Maxplus2 directory).Is something I can find eslewhere or I have to build the symbol/design file myself?The logic diagram of the 74245 is well done in every manufacturer datasheet, I attach it here for reference.Thanks in advance for any help.

Lien copié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

I am not sure which Intel FPGA product that you are using but the FPGA device itself should already contains the transceiver channel if it's supported in the device.

You shouldn't be creating your own transceiver design logic as it's meant to be hard circuitry designed in the silicon already. What user should do it is

- use the megawizard or IP catalog to instantiate transceiver channel for design usage

- The are different type of transceiver IP solution available on each FPGA device. User can pick the one that suit their design requirement

Thanks.

Regards,

dlim

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Thanks for reply.I'm not targeting Intel FPGAs but old Altera CPLDs.The transceiver is connected to the the data bus of an external RAM hence, even if I desgn my own transceiver, then I have the problem of how to interface the RAM to internal logics of the CPLD.Sorry but I'm new to HDL and all I can do for now is doing designs using schematics block (which is not the same thing of writing HDL hence it could not work)

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

Like I said, you need to use either megawizard or IP catalog in the Quartus software to instantiate the transceiver channel so that you can connect the transceiver channel on CPLD to CPLD internal logic.

megawizard and IP catalog support both HDL design and graphical symbol design. The transceiver IP will generate a BSF schematic symbol that you can add in your BDF design later.

Thanks.

Regards,

dlim

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

I made my own schematics .BDF design and .BSF symbol for the 74245, I attach them, perhaps someone can check if design has the correct logics.

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

I get a better idea what you are doing now. Basically you are trying to design a circuit function called "74245 octal transceiver" and connect to FPGA IO pins.

I feel unless someone in this forum community is familiar with "74245 octal transceiver" else it's hard for people to comment on your design correctness.

My suggestion to you is perhaps you can run functional simulation to test out your design functionality. This is a better and universal way to verify user design.

Thanks.

Regards,

dlim

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

HI,

I didn't hear back from you.

Hopefully you are able to verify your design using simulation.

For now, I am setting this case to closure.

Regards,

dlim

- S'abonner au fil RSS

- Marquer le sujet comme nouveau

- Marquer le sujet comme lu

- Placer ce Sujet en tête de liste pour l'utilisateur actuel

- Marquer

- S'abonner

- Page imprimable