- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was looking for a complex multiplication, and found in the Quartus in IP Catalog, Library/Basic Functions/Arithmetric the ALT_MULT_COMPLEX.

I used it with a enable, let it produce a VHD file.. during compile if showed errors,

there where END IF's missing.

And looking further... there are only 3 mulltiplies used in the code..

But of course a full complex multiplication need 4 multiplies.

So the ALT_MULT_COMPLEX can not be used..

Do I need to pick an other IP ?

Best regards,

Theo Mulder

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi FvM,

Thanks for your reply..,

I already build my own complex multiplication, so i'm fine.

But to show the problem.., i attached the *.vhd file that was generated by the ALT_MULT_COMPLEX -IP.

at least one problem is: the IF (ena = '1') THEN do not have a closing END IF.

I used Quartus Prime Lite 22.1std. And used a Cyclone V

Kind Regards,

Theo Mulder

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Theo,

I can confirm that the generated VHDL code doesn't compile due to syntax errors, the Verilog code is however syntactically correct.

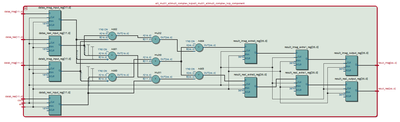

Regarding usage of 3 multipliers, I'm not sure, but I guess it may be an alternative algorithm to calculate complex multiply. I didnt check the results. Here's the RTL schematic, if anyone knows about the algorithm.

Regards

Frank

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for pointing the defect. I have raised this concern to the engineering team.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The issue has been acknowledged by the engineering team and will be fixed in future version of Quartus software. There will be a Knowledge Article published for the issue, so that all users are made aware of. Meanwhile, we request you to continue using the Verilog model of the IP as a workaround.

As there are no further queries on this topic, I am closing the case.

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page