- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, I'm looking to investigate the setup times for a design I have. However, despite following AN 775 as best I as I can, I am not generating any outputs from my design. Instead all I see are two Data ports which I haven't declared myself in my design...

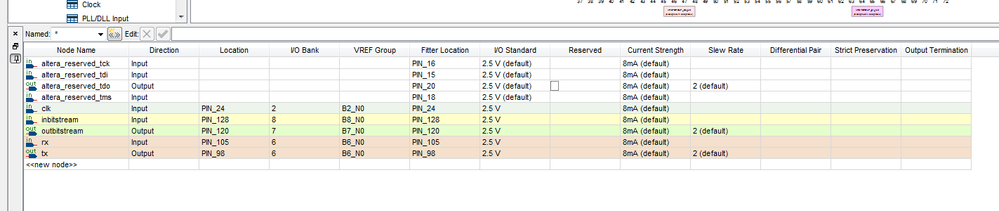

Here is the pin planner - it shows these extra pins, but also my own data ports.

Furthermore here are my declared ports in my top level file.

module bertfront(

input clk,

input inbitstream,

input [1:0] control, //[1] start, [0] reset

output outbitstream,

output reg ledstatus,

output reg [31:0] totalbits,

output reg [31:0] incorrectbits

);

Can anyone shed some light as to why I'm not seeing my own data ports in the timing analysis? If you need any more code I would be happy to share the entire project.

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ted,

When we debug your design with the JTAG interface, the JTAG signals TCK, TMS, TDI, and TDO are implemented as part of the design.

The altera_reserved_tck/tms/tdi pin is automatically generated for a design that uses a JTAG accessible module such as the Nios II debugger, SignalTap II logic analyzer, and In-System Memory Content Editor.

For timing constraint those pins

To constrain this JTAG clock, apply a 33-MHz clock constraint to this pin.

For the TimeQuest Timing Analyzer, use the following command:

create_clock -period "30.303 ns" -name {altera_reserved_tck} {altera_reserved_tck}

Reference

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd04282008_867.html

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_timequest_cookbook.pdf

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand