- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I have a design where I generate an SPI clock and send some data over the slave. The slave is an ADC with its own setup/hold time constraints. In these constraints, the slave data input SDI has constraints with respect to the SCLK, but I'm not sure how to properly constraint that. What I did so far is that I constrainted the SCLK on its own as if it's a data output of the FPGA and then constraint the MOSI with referencing the SCLK. The syntax I used in the sdc file is added below.

# main clock of the FPGA

create_clock -name {clk} -period 100MHz [get_ports {clk}]

# Specify generated clock from PLL (PLL output is 100MHz)

# set_instance_assignment -name corepll_inst|altpll_component|auto_generated|pll1 -to pll_inst

# create_generated_clock -name {pll_clk} -source [get_pins pll_inst|clk[0]] -divide_by 1

# constraints for SCLK and MOSI

set_output_delay -clock {corepll_inst|altpll_component|auto_generated|pll1|clk[0]} -max 3 [get_ports {SCLK1}]

set_output_delay -clock {corepll_inst|altpll_component|auto_generated|pll1|clk[0]} -min -2 [get_ports {SCLK1}]

set_output_delay -clock {corepll_inst|altpll_component|auto_generated|pll1|clk[0]} -reference_pin SCLK1 -max 5 [get_ports {MOSI1}]

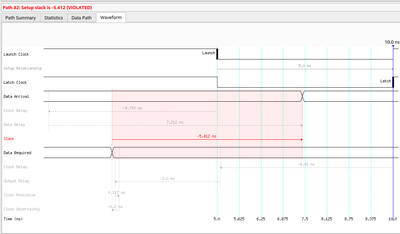

set_output_delay -clock {corepll_inst|altpll_component|auto_generated|pll1|clk[0]} -reference_pin SCLK1 -min -5 [get_ports {MOSI1}]What I observe in the Timing Analyzer is that the setup and hold times are not the only things when checking the timing analyzer. For the example that you can see on the snippet attached, I would expect that the data required for the setup time of SCLK1 would be only 3 ns far from the latch clock's posedge, where the cursor is. I'm almost sure that what I want to achieve does not match with the constraints I used, therefore I'd like to ask what I'm doing wrong or missing.

Any help is much appreciated,

Cheers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Adding the pins of the Quad SPI IP did not work, but generating another clock like this and constraining the other QSPI ports wrt. this clock seems to work somehow

create_generated_clock -name {qclk_vclk} -source [get_pins {corepll_inst|altpll_component|auto_generated|pll1|clk[0]}] [get_ports {QSPI_CLK}]

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there, the generated clock constraints are ignored which causes your out/input delay constraint are invalid:

Seems that the pll_inst doesn't exist, so there is no source clock for the create generated clock constraint which causes the issue:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you shared any media/link after eah line of yours, they're not visible. I opened this thread in 3 different web browsers to see what you've shared in this response, but I couldn't see anything.

The `pll_inst` in the .sdc file is just a name that I made up, just to make easy to use the PLL's clock output in the whole .sdc file (you can also see that in this line below in the .sdc).

set_instance_assignment -name corepll_inst|altpll_component|auto_generated|pll1 -to pll_inst

You said that the `pll_inst` does not exist, but I can clearly see the corepll component (with the name `corepll_inst`) in the project. The component itself used in the project can be found under "IP Catalog -> Library -> Basic Functions -> Clocks; PLL and Resets -> PLL -> ALTPLL " and it's also instantiated in my top level .vhd file. So there must be another reason why the `pll_inst` doesn't seem to exist..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there, I see. In your SDC file:

create_generated_clock \

-name {qclk} [get_ports {QSPI_CLK}]\

-source [get_fanins {QSPI_CLK}] \

-divide_by 1 \

'get fanins' can't be applied here as it will return a collection with more than one objects which can't be the source.

BTW, set_instance_assignment also can't be used in SDC file which will be ignored, you may apply it in your QSF and try again or directly use the original name instead of 'pll_inst'.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the response. What do you suggest instead of `get_fanins` ? I wanted to create a virtual clock here from the generated QSPI output clock so that I can use it in my constraints.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is not how a virtual clock created. Please follow the UG 2.6.5.2:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I upload the user guide here

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @TingJiangT_Intel ,

I don't get how I can do what I've described in this entry with virtual clocks then. Because I wanted to use the sclk1 outputs to check the timing of some certain ports. What would be the right approach here ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not really quiet understand what you mean by 'use the sclk1 outputs to check the timing of some certain ports'. Based on the current SDC file the main problem is the clocks you created are ignored.

If you want to create a virtual clock you can use the 'create_clock' constraint.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What I meant by that is this: I want the SCLK1 clock output to be used for checking the setup/hold time violations of MOSI1 and MISO1 ports for example. The setup/hold time requirements are given by the manufacturer of the external chip. But at the same time, I want to check SCLK1, MISO1 and MOSI1 with respect to the pll clock to verify that the timing is right for the FPGA itself as well as the external device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Currently, you output/input delay constraints are invalid due to the previous problem we discussed which caused these paths unconstraint, and the software won't analyze these paths.

You need to first fix the issue of ignored constraints.

Please apply 'set_instance_assignment -name corepll_inst|altpll_component|auto_generated|pll1 -to pll_inst' to the qsf file instead of sdc file. Or you can directly use 'corepll_inst|altpll_component|auto_generated|pll1' instead of pll_inst.

And don't use get_fanin to get the source clock, please try to use wire_pll1_clk[0]~clkctrl as the source clock of qclk.

I can't apply changes to your sdc file, so please try the modification from your side.

Hope this can help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Should I use `get_nets` then to use that wire ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can try 'get_pins'.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can try the following setting:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Adding the pins of the Quad SPI IP did not work, but generating another clock like this and constraining the other QSPI ports wrt. this clock seems to work somehow

create_generated_clock -name {qclk_vclk} -source [get_pins {corepll_inst|altpll_component|auto_generated|pll1|clk[0]}] [get_ports {QSPI_CLK}]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

-

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »