- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Quartus Support Team,

Attaching the screen-shot from the "L- and H-tile Avalon® Streaming and Single Root I/O Virtualization (SRIOV) Intel® FPGA IP for PCI Express* User Guide" Table 43.

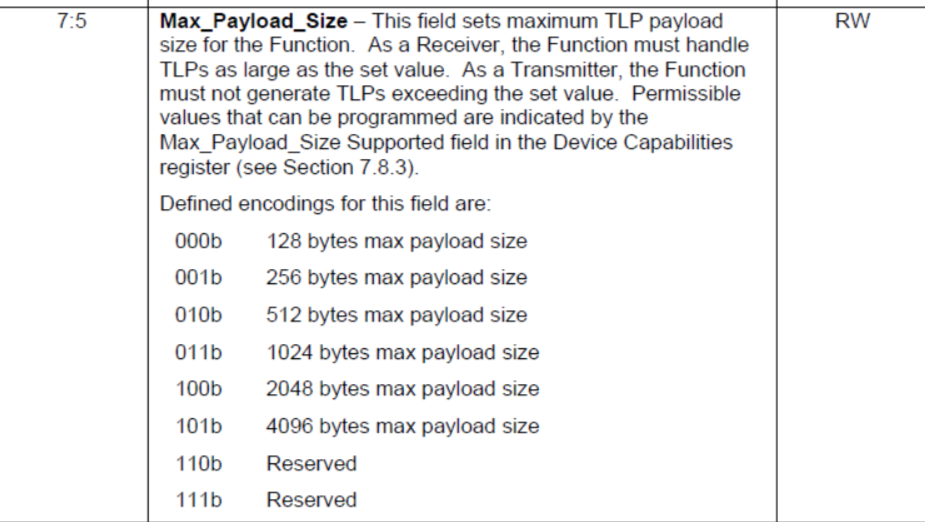

What is the encoded value of [2:0] Max payload size ?

is it something as follows -

000 -128Byte

001- 256Byte

010- 12Bytes

011-1024Byte

-----

------ or different ?

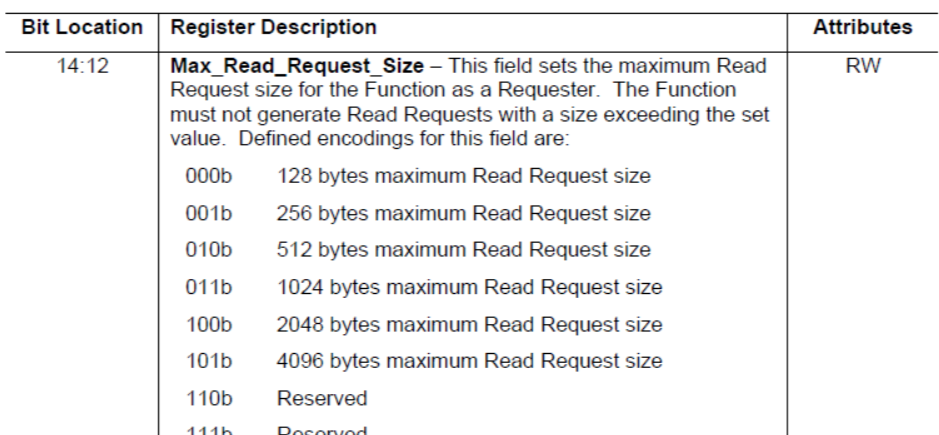

Also what is the encoded value in [5:3] Max rd req size ??

Please share more details about the encoded value of this 2 signals

[5:3] Max rd req size

[2:0] Max payload size

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for correcting me, my apologize for misunderstanding the question.

For your information the spec is not owned by intel, it is a general spec that all PCIe IP need to follow.

You can get the detail in "PCI Express® Base Specification" in the web.

For your question, I do help to printscreen it to you.

Max rd req size

Max payload size

Hope this answer your question, Let me know if this is helpful to you.

Regards,

Wincent_Intel

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for reaching out.

Just to let you know that Intel has received your support request and I am assigned to work on it.

Allow me some time to look into your issue. I shall come back to you with findings.

Thank you for your patience.

Best regards,

Wei Chuan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

From low level description, it is part of the Transaction Layer (TL) bus provides a subset of the information stored in the Configuration Space. Those Information on the Transaction Layer (TL) bus is time-division multiplexed (TDM). When tl_cfg_func[1:0]= 2'b00, tl_cfg_ctl[31:0] drives PF0 Configuration Space register values for eight consecutive cycles. The next 40 cycles are reserved. Then, the 48-cycle pattern repeats as per mention in the user guide.

Can I know is there any specific reason asking that question ? do you facing problem on the configuration ?

Regards,

Wincent_Intel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

The text you copy and pasted is from user guide, that we have gone through.

There is no issue of configuration. I just want to use this two following signal for our design.

[5:3] Max rd req size

[2:0] Max payload size

Actual question to make you more clear-

question:- Please share more details about the encoded value of this signals ( [5:3] Max rd req size [2:0] Max payload size ). What does each state means ?

Please don't copy paste the user guide content, We have gone through that but nothing is listed there properly.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for correcting me, my apologize for misunderstanding the question.

For your information the spec is not owned by intel, it is a general spec that all PCIe IP need to follow.

You can get the detail in "PCI Express® Base Specification" in the web.

For your question, I do help to printscreen it to you.

Max rd req size

Max payload size

Hope this answer your question, Let me know if this is helpful to you.

Regards,

Wincent_Intel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Piyush,

Thanks for your reply, With that said I will close this case on my place.

The community users will be able to help you with your follow-up questions.

If you have new problem, feel free to open another community thread.

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or please let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I wish to follow up with you about this case.

I believe my previous reply answered your question, Do you have any further questions on this matter ?

Else I would like to have your permission to close this forum ticket

Regards,

Wincent_Intel