- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Im trying to build a project that contains a lot of sub modules in quartus and, trying to debug the system because of a supposedly malfunctioning module, I found out that, if I compile the whole project, the result for that said module is missing some inputs (when observed on the RTL viewer) if compared to the result for the module compiled alone.

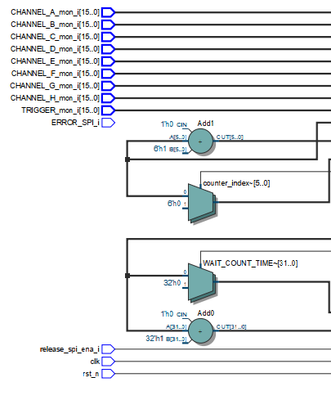

As can be seen in the first image, if I compile the module alone using his file as the top level all the input appears correctly in the RTL Viewer.

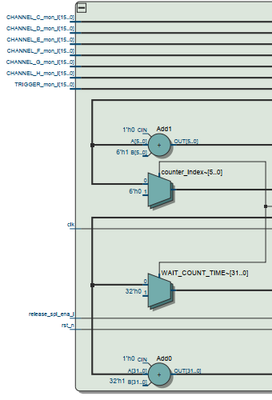

But if I compile the whole project, in the RTL Viewer to the corresponding module I get the result in the following image. In which its missing the entries CHANNEL_A_mon_i and CHANNEL_B_mon_i.

I don't know if it's because I'm using too many blocks or if something is interacting wrongly.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

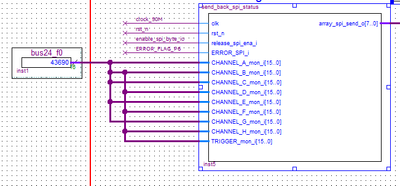

Well if that indeed is your top level schematic, you have wired channels A...H and the trigger all to the same 16b bus.

So it is not surprising at all that logic is eliminated.

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

When compiled as a top module, all inputs and outputs are assumed to be used by Quartus, and the logic is generated.

Once instantiated as a sub module, Quartus can detect unused logic paths, and remove them.

Probably what you are seeing happen.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Oh, I see.

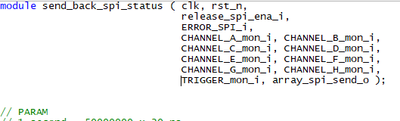

At first, I thought there was some misconnection in the system, but my knowledge of quartus with block diagram is limited, so I didn't find a proper way of checking. Given that I'm using symbols in the block diagram with Verilog code as shown in the images below, do you have any suggestions?

Thank you so much for the reply,

Best regards,

Hugo Stein

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Well if that indeed is your top level schematic, you have wired channels A...H and the trigger all to the same 16b bus.

So it is not surprising at all that logic is eliminated.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Well, it did, but the issue my colleague acknowledged above wasn't the root problem.

I was using a problematic parameter register, which had been truncated for some reason, and thus some inputs, in this case CHANNEL_A_mon_i and CHANNEL_B_mon_i, were not properly connected, leaving some unused logic paths as mentioned before.

Also, @_AK6DN_ said that connecting several paths to the same buffer would create redundant logic that would later be eliminated by the compiler. But now seeing the problem I disagree with that statement.