- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

i get the following message "Error (171011): Can't assign node "FPGA_CLK1_50" to location PIN_AF14 -- node is type Combinational cell

" when i try to assign pins using the pin assignment.

After a bit of searching i see that it used to be an error that happens in older quartus version and for Stratix iii fpga family. However i use quartus 17.1 and Cyclone V device family.

Another point is that i get this error only when using the HLS(high level synthesis) generated ip to connect to a top level verilog module.

It would be great if someone can give me an idea on how to solve this problem.

Many thanks in advance

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raj,

I was trying to understand the problem, You have generated a IP using HLS, integrated it in top module and trying to assign a pin which gives you error? Am i right?

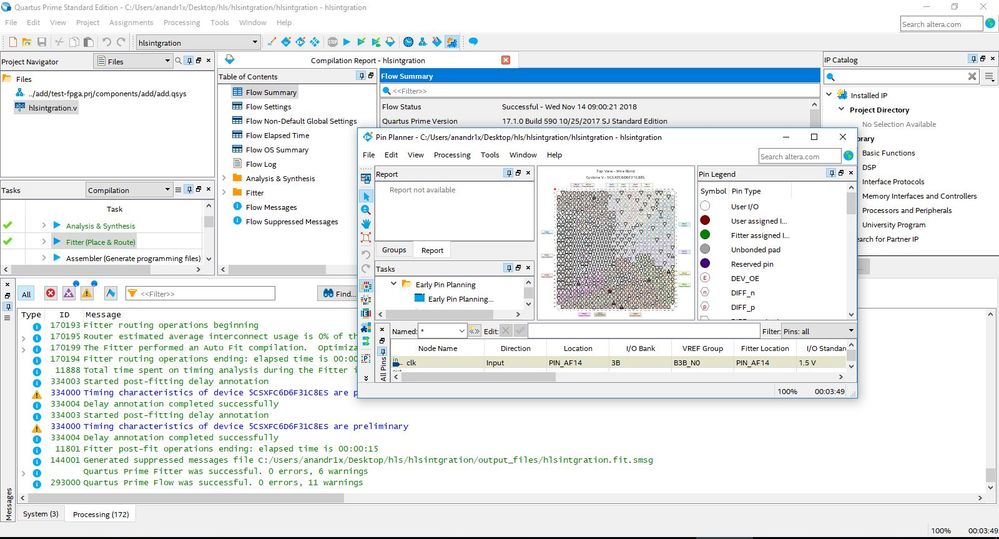

We have tried the same with the simple add example for which .IP/.QSYS file is created using HLS and we have used Quartus 17.1 std for integration to top module and assigned a clock pin to AF14 for Cyclone V device 5CSXFC6D6F31C8ES. Attached cmd log and image.

I was not-able to successful replicate the Error mentioned.

However if you can share your .cpp file i can try from my side.

And can you remove the pin assignments and check if fitter is able to place the design successfully with its default assignments

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards,

Anand Raj Shankar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raj,

The possible reason for the issue you faced is using Quartus design generated by HLS compiler and re-assigning virtual pins to physical ones with the Assignment Editor.

Based on my experience, the Assignment Editor might not remove virtual pin assignments from *.qsf file but hide them in its GUI window. Having both virtual and physical pins assigned to the port results in error message "Error (171011): Can't assign node "PIN_..." to location -- node is type Combinational cell." Please search .qsf file of your project in the text editor and comment out/remove undesirable virtual pin assignments.

Regards,

Igor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page