- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

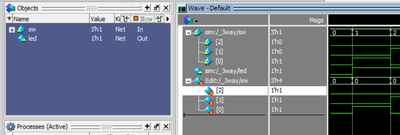

I am trying to run timing simulation in Questa Sim Intel Starter Edition (Quartus Prime Lite v22.1.1). After fitting, the compilation is correctly done and also the timing simulation is executed without errors. However, when I open the wave.do file the input variables appear with a red icon as shown in the figure. No output variable is displayed. When I press ‘Run All’, the saved input signals appear though no output signal. Above the variables with the red icon, all variables (including the output) appear as if a functional simulation was conducted (no delays shown).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for this information. I will definitely look into it.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I forgot to mention that I am using the DE0-CV board and I am referring to the directory

C:/intelFPGA_lite/22.1std/questa_fse/intel/verilog/cyclonev

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Gate-level timing simulation is supported only for the Arria II GX/GZ, Cyclone IV, MAX II, MAX V, and Stratix IV device families.

Unfortunately, the gate-level timing simulation is Not supported for Cyclone V device.

Reference: https://www.intel.com/content/www/us/en/docs/programmable/683080/22-1/simulation-levels.html

We recommend that you use Timing Analyzer tool available in Quartus, to verify the timing performance of a design.

You may checkout the User Guide below on how-to use the Timing Analyzer:

https://www.intel.com/content/www/us/en/programmable/documentation/ony1529966370740.html

Best Regards,

Richard Tan

p/s: If you find any answers from the community or Intel Support to be helpful, we encourage you to mark them as the best answer or rate them 4/5 in the survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dropping a note to ask if my last reply was helpful to you?

Do you need any further assistance from my side?

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer. It is indeed a pity that both Cyclone V and MAX 10 devices are not supported It surprises me since these are included on the development boards of Terasic.

Anyway, I will try the Timing Analyzer tool available in Quartus and let you know hoe I am getting on with that one.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sure, do let me know if you have further question.

I am happy to helps.

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am an educator and preparing a hands-on tutorial on Quartus Prime for first time users. I had a look at Timing Analyzer and found it too involved for an introductory course I am afraid.

BTW: I also posted another question on this forum, namely "USB Blaster cannot be selected". If it fits with your schedule, I would appreciate it if you could have a look at that one as well.

With Thanks and Best Regards,

Karel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If the topic is too complicated, you may start with University Self-Guided Lab: Introduction to Static Timing Analysis of Digital Circuit and Understanding Timing Analysis in FPGAs.

Then slowly move forward with other in-depth courses like.

1. Intel® Quartus® Prime Pro Software Timing Analysis – Part 1: Timing Analyzer

2. Intel® Quartus® Prime Pro Software Timing Analysis – Part 2: SDC Collections

3. Intel® Quartus® Prime Pro Software Timing Analysis – Part 3: Clock Constraints

4. Intel® Quartus® Prime Pro Software Timing Analysis – Part 4: I/O Interfaces

5. Intel® Quartus® Prime Pro Software Timing Analysis – Part 5: Timing Exceptions

I also recommend to attend the instructor-led training. Please note that the training will be based on Quartus Pro.

You can find more courses @ https://learning.intel.com/developer/pages/30/all-intel-developer-training

I saw that an agent have been assigned to your other forum case. You should expect a reply soon.

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for this information. I will definitely look into it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm glad to hear that your question has been addressed. Now, I will transition this thread to community support. If you have any further questions or concerns, please don't hesitate to reach out.

Thank you and have a great day!

Best Regards,

Richard Tan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page