- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello, I am trying to create a testbench for a mips processor in VHDL. It compiles fine in quartus and in modelsim but when I try to start the simulation I get this error.

* Error: (vsim-3732) D:/Quartus/4712labvhd/top_level.vhd(169): No default binding for component instance 'UUT_CON'.

# The following component port is not on the entity:

# IR31_to_26

Anything Helps. The first bit of code is the testbench itself and the next is the top level entity that I use inside.

library ieee;

use ieee.std_logic_1164.all;

entity top_level is

generic(

WIDTH : positive := 32

);

port (

clk : in std_logic;

buttons : in std_logic_vector(1 downto 0);

switches : in std_logic_vector(9 downto 0);

led0 : out std_logic_vector(6 downto 0);

led0_dp : out std_logic;

led1 : out std_logic_vector(6 downto 0);

led1_dp : out std_logic;

led2 : out std_logic_vector(6 downto 0);

led2_dp : out std_logic;

led3 : out std_logic_vector(6 downto 0);

led3_dp : out std_logic;

led4 : out std_logic_vector(6 downto 0);

led4_dp : out std_logic;

led5 : out std_logic_vector(6 downto 0);

led5_dp : out std_logic

);

end top_level;

architecture STR of top_level is

signal ADDRESS : std_logic_vector(31 downto 0);

signal ALUOp : std_logic_vector(5 downto 0) ;

signal IR31_to_26: std_logic_vector(5 downto 0);

signal alu_out, alu_out_hi, A_out, B_out, regfileout1, regfileout2, MemoryRegOut, WRdata_out, HI_out, LO_out: std_logic_vector(31 downto 0);

signal ALUSrcB, PCSource, ALU_LO_HI : std_logic_vector(1 downto 0);

signal OPSelect: std_logic_vector(5 downto 0);

signal PCWriteCond, PCWrite, IorD, MemRead, MemWrite, IRWrite, MemToReg, JumpAndLink, IsSigned, ALUSrcA, RegWrite, RegDst : std_logic;

signal inport_en, reset_en:std_logic;

signal OutPort_int:std_logic_vector(31 downto 0);

signal switch_int: std_logic_vector(31 downto 0);

component controller is

generic (

width : positive := 32);

port (

clk : in std_logic := '0';

rst : in std_logic := '0';

PCWriteCond : out std_logic;

PCWrite : out std_logic;

IorD : out std_logic;

MemRead : out std_logic;

MemWrite : out std_logic;

MemToReg : out std_logic;

IRWrite : out std_logic;

JumpAndLink : out std_logic;

IsSigned : out std_logic;

PCSource : out std_logic_vector(1 downto 0);

ALUOp: out std_logic_vector(5 downto 0) ;

IR31_to_26 : in std_logic_vector(5 downto 0) ;

ALUSrcB : out std_logic_vector(1 downto 0);

ALUSrcA : out std_logic;

RegWrite : out std_logic;

RegDst : out std_logic

);

end component;

component datapath is

generic (

width : positive := 32);

port (

clk : in std_logic;

rst : in std_logic;

switches: in std_logic_vector(31 downto 0);

buttons: in std_logic_vector(1 downto 0);

PCWriteCond : in std_logic;

PCWrite : in std_logic;

IorD : in std_logic;

MemRead : in std_logic;

MemWrite : in std_logic;

MemToReg : in std_logic;

IRWrite : in std_logic;

JumpAndLink : in std_logic;

IsSigned : in std_logic;

PCSource : in std_logic_vector(1 downto 0);

ALUOp : in std_logic_vector(5 downto 0) ;

IR31_to_26 : out std_logic_vector(5 downto 0) ;

ALUSrcB : in std_logic_vector(1 downto 0);

ALUSrcA : in std_logic;

RegWrite : in std_logic;

RegDst : in std_logic;

OutPort : out std_logic_vector(31 downto 0)

);

end component;

component decoder7seg is

port (

input : in std_logic_vector(3 downto 0);

output : out std_logic_vector(6 downto 0));

end component;

-- signals for top_level

signal input1 : std_logic_vector(8 downto 0);

signal input2 : std_logic_vector(8 downto 0);

signal output_internal : std_logic_vector(6 downto 0);

begin

inport_en <= not buttons(0);

reset_en <= not buttons(1);

switch_int <= "0000000000000000000000" & switches;

-- map adder output to two LEDs

U_LED5 : decoder7seg port map (

input =>OutPort_int(23 downto 20),

output => led5);

U_LED4 : decoder7seg port map (

input => OutPort_int(19 downto 16),

output => led4);

-- all other LEDs should display 0

U_LED3 : decoder7seg port map (

input => OutPort_int(15 downto 12),

output => led3);

U_LED2 : decoder7seg port map (

input => OutPort_int(11 downto 8),

output => led2);

U_LED1 : decoder7seg port map (

input => OutPort_int(7 downto 4),

output => led1);

U_LED0 : decoder7seg port map (

input => OutPort_int(3 downto 0),

output => led0);

UUT_CON : controller

port map(

clk => clk,

rst =>reset_en,

PCWriteCond => PCWriteCond,

PCWrite => PCWrite,

IorD => IorD,

MemRead => MemRead,

MemWrite => MemWrite,

MemToReg => MemToReg,

IRWrite => IRWrite,

JumpAndLink => JumpAndLink,

IsSigned => IsSigned,

PCSource => PCSource,

ALUOp => ALUOp,

IR31_to_26 => IR31_to_26,

ALUSrcB => ALUSrcB,

ALUSrcA => ALUSrcA,

RegWrite =>RegWrite,

RegDst => RegDst

);

UUT_DATA : datapath

port map(

clk => clk,

rst =>reset_en,

switches => switch_int,

buttons => buttons,

PCWriteCond => PCWriteCond,

PCWrite => PCWrite,

IorD => IorD,

MemRead => MemRead,

MemWrite => MemWrite,

MemToReg => MemToReg,

IRWrite => IRWrite,

JumpAndLink => JumpAndLink,

IsSigned => IsSigned,

PCSource => PCSource,

ALUOp => ALUOp,

IR31_to_26 => IR31_to_26,

ALUSrcB => ALUSrcB,

ALUSrcA => ALUSrcA,

RegWrite =>RegWrite,

RegDst => RegDst,

OutPort => OutPort_int

);

end STR;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

entity mips_tb is

end mips_tb;

architecture TB of mips_tb is

component top_level is

generic(

WIDTH : positive := 32

);

port (

clk : in std_logic;

buttons : in std_logic_vector(1 downto 0);

switches : in std_logic_vector(9 downto 0);

led0 : out std_logic_vector(6 downto 0);

led0_dp : out std_logic;

led1 : out std_logic_vector(6 downto 0);

led1_dp : out std_logic;

led2 : out std_logic_vector(6 downto 0);

led2_dp : out std_logic;

led3 : out std_logic_vector(6 downto 0);

led3_dp : out std_logic;

led4 : out std_logic_vector(6 downto 0);

led4_dp : out std_logic;

led5 : out std_logic_vector(6 downto 0);

led5_dp : out std_logic

);

end component;

signal output_PC : std_logic_vector(31 downto 0) := (others => '0');

signal clock_int : std_logic:='0';

signal data_int : std_logic_vector (31 downto 0);

signal wren_int : std_logic ;

signal q_int : std_logic_vector (31 downto 0);

signal reset_int :std_logic;

signal mux_sel : std_logic_vector(1 downto 0);

signal buttons_int : std_logic_vector(1 downto 0);

signal switches_int : std_logic_vector(9 downto 0);

begin

UUT_top : top_level

port map(

clk => clock_int,

buttons => buttons_int,

switches => switches_int

);

clock_int <= not clock_int after 10 ns;

process

begin

reset_int <='1';

wait for 50 ns;

reset_int <='0';

wait for 50 ns;

end process;

end TB;

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi @CPaul

Can you attach complete project. So that we can simulate in our side once and check.

Regards

Anand

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi @CPaul ,

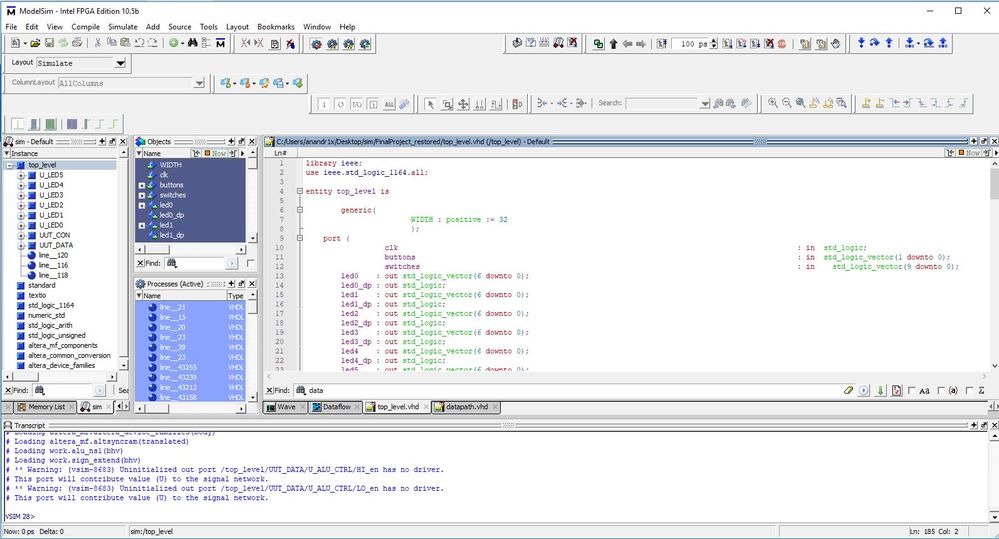

I can simulate your design without any error

Compile all the vhd files again in proper order try.

attached transcript from which you can find the information on error which i have faced because of compile order and image.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I am a bit confused on how to actually read the transcript for what the compile order of my files should be. is it possible you could tell me what files you included in the compilation and what order they were in on modelsim?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

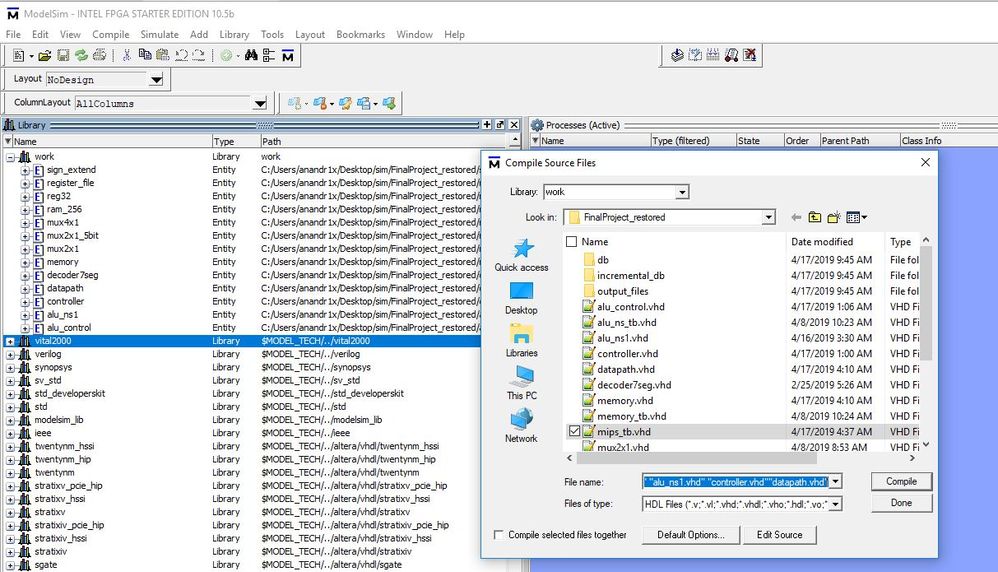

Hi @CPaul ,

Order "decoder7seg.vhd" "memory.vhd" "mux2x1.vhd" "mux2x1_5bit.vhd" "mux4x1.vhd" "ram_256.vhd" "reg32.vhd" "register_file.vhd" "sign_extend.vhd" "alu_control.vhd" "alu_ns1.vhd" "controller.vhd""datapath.vhd" which worked. copy past it in file name under compile source file tab.

For error which you have you have to compile controller .vhd and run simulation.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi @CPaul,

Yes, I was able to see the clock running.

- Uninitialized out port has no driver check your design and its mapping.

- place week2_demo.mif in simulation directory.

Regards

Anand